# RK3568 Hardware Design Guide

Release Version: V1.2 Release Date: 2022-01-26

2004

#### DISCLAIMER

THIS DOCUMENT IS PROVIDED "AS IS". ROCKCHIP ELECTRONICS CO., LTD.("ROCKCHIP")DOES NOT PROVIDE ANY WARRANTY OF ANY KIND, EXPRESSED, IMPLIED OR OTHERWISE, WITH RESPECT TO THE ACCURACY, RELIABILITY, COMPLETENESS,MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE OR NON-INFRINGEMENT OF ANY REPRESENTATION, INFORMATION AND CONTENT IN THIS DOCUMENT. THIS DOCUMENT IS FOR REFERENCE ONLY. THIS DOCUMENT MAY BE UPDATED OR CHANGED WITHOUT ANY NOTICE AT ANY TIME DUE TO THE UPGRADES OF THE PRODUCT OR ANY OTHER REASONS.

#### **Trademark Statement**

"Rockchip", "瑞芯微", "瑞芯" shall be Rockchip's registered trademarks and owned by Rockchip. All the other trademarks or registered trademarks mentioned in this document shall be owned by their respective owners.

#### All rights reserved. ©2020. Rockchip Electronics Co., Ltd.

Beyond the scope of fair use, neither any entity nor individual shall extract, copy, or distribute this document in any form in whole or in part without the written approval of Rockchip.

瑞芯微电子股份有限公司 Rockchip Electronics Co., Ltd. Address: No. 18 Building, A District, No.89, software Boulevard Fuzhou, Fujian, PRC Website: <u>www.rock-chips.com</u> Customer service tel.: +86-4007-700-590 Customer service fax: +86-591-83951833 Customer service e-mail: <u>FAE@rock-chips.com</u>

Rockc

# Preface

#### **Overview**

This document presents the key points of hardware design and notices for RK3568 processors, aiming to help customers shorten developing period of product, improving product design stability and reducing fault rate. Please refer to the requirements of this guide for hardware design, and use the relevant core templates released by Rockchip. If you need to modify for special reasons, please strictly follow the design rule of ridentia high-speed-digital-circuit and Rockchip Schematic&PCB checklist requirements.

#### **Chipset Model**

This document is suitable for the following chipset model: RK3568

#### **Intended Audience**

This document (this guide) is mainly intended for:

- Hardware development engineers

- Layout engineers

- Technical support engineers

- Test engineers •

# **Revision History**

This revision history recorded description of each version, and any updates of previous versions are included in the latest one.

| Version<br>No. | Author  | Revision<br>Date | Revision Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Remark |

|----------------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| V1.2           | Zhangdz | 2021-10-14       | 1:Update the description of ECC (Section 2.1.7.2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| V1.1           | Zhangdz | 2021-06-08       | <ol> <li>Update the description of wake-up and standby of<br/>infrared receiver (Section 2.3.17)</li> <li>Add IO Domain power supply and software<br/>configuration attentions (Section 2.1.11)</li> <li>Update the DCDC power supply capacity requirements<br/>of VDD_NPU and VDD_LOGIC power supplies, which<br/>require 2A or more (Section 2.2.2.6 and 2.2.2.7)</li> <li>VDD_LOGIC peak current is updated to 1.2A (Section<br/>2.2.6)</li> <li>Add a description of the module that does not supply<br/>power, and the corresponding node in DTS should be<br/>disabled (Section 2.2.2.1)</li> </ol> |        |

| V1.0           | Zhangdz | 2021-04-16       | The initial release version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                |         |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|                |         |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

Rocken

# Acronyms

Acronyms include the abbreviations of commonly used phrases in this document:

| ARM           | Advanced RISC Machine                   | 享仍特简指众生计算机                           |

|---------------|-----------------------------------------|--------------------------------------|

|               |                                         | 高级精简指令集计算机                           |

| CAN           | Controller Area Network                 | 控制器局域网络                              |

| CEC           | Consumer Electronics Control            | 消费电子控制                               |

| CIF           | Camera Input Format                     | 相机并行接口                               |

| CPU           | Central processing unit                 | 中央处理器                                |

| CSI           | Camera Serial Interface                 | 相机串行接口                               |

| DC/DC         | Direct current-Direct current converter | 直流/直流变换器                             |

| DDR           | Double Data Rate                        | 双倍速率同步动态随机存储器                        |

| DP            | DisplayPort                             | 显示接口                                 |

| DSI           | Display Serial Interface                | 显示串行接口                               |

| EBC           | E-book controller                       | 电子书控制器                               |

| eDP           | Embedded DisplayPort                    | 嵌入式数码音视讯传输接口                         |

| eMMC          | Embedded Multi Media Card               | 内嵌式多媒体存储卡                            |

| ESD           | Electro-Static discharge                | 静电释放                                 |

| ESR           | Equivalent Series Resistance            | 等效电阻                                 |

| Flash_VOL_SEL | Flash voltage selection                 | eMMC/Nand Flash IO电压选择               |

| FSPI          | Flexible Serial Peripheral Interface    | 灵活串行外设接口                             |

| GPU           | Graphics Processing Unit                | Figure形处理单元                          |

| HDMI          | High Definition Multimedia Interface    | 高清晰度多媒体接口                            |

| HPD           | Hot Plug Detect                         | 热插拔检测                                |

| I2C           | Inter-Integrated Circuit                | 内部整合电路(两线式串行通讯总<br>线)                |

| I2S           | Inter-IC Sound                          | 集成电路内置音频总线                           |

| ISP           | Image Signal Processing                 | Figure像信号处理                          |

| JTAG          | Joint Test Action Group                 | 联合测试行为组织定义的一种国际标准测试协议(IEEE 1149.1兼容) |

| LDO           | Low Drop Out Linear Regulator           | 低压差线性稳压器                             |

| LCDC          | LCD Controller                          | LCD 控制器并行接口                          |

| LCM           | LCD Module                              | LCD显示模组                              |

| LVDS          | Low-Voltage Differential Signaling      | 低电压差分信号                              |

| MAC           | Media Access Control                    | 以太网媒体接入控制器                           |

| MIPI          | Mobile Industry Processor Interface     | 移动产业处理器接口                            |

| NPU           | Neural network Processing Unit          | 神经网络处理器                              |

| РСВ           | Printed Circuit Board                   | 印制电路板                                |

| KKJJ00 Huruw | are Design Guide                                              | KeV V 1.2               |

|--------------|---------------------------------------------------------------|-------------------------|

| PCIe         | Peripheral Component Interconnect<br>-express                 | 外设组件互联标准                |

| РСМ          | Pulse Code Modulation                                         | 脉冲编码调制                  |

| PDM          | Pulse density modulation                                      | 脉冲密度调制                  |

| PLL          | Phase-locked loop                                             | 锁相环                     |

| PMIC         | Power Management IC                                           | 电源管理芯片                  |

| PMU          | Power Management Unit                                         | 电源管理单元                  |

| PWM          | Pulse width modulation                                        | 脉冲宽度调制                  |

| QSGMII       | Quad Serial Gigabit Media Independent Interface               | 四串行千兆媒体独立接口             |

| RGB          | RGB color mode is a color standard in industry                | RGB色彩模式,是工业界的一种颜<br>色标准 |

| GMAC         | Gigabit Media Access Controller                               | 千兆媒体访问控制器               |

| RGMII        | Reduced Gigabit Media Independent Interface                   | 简化千兆媒体独立接口              |

| RMII         | Reduced Media Independent Interface                           | 简化媒体独立接口                |

| RK           | Rockchip Electronics Co.,Ltd.                                 | 瑞芯微电子股份有限公司             |

| SARADC       | successive approximation register Analog to digital converter | 逐次逼近寄存器型模数转换器           |

| SATA         | Serial Advanced Technology Attachment                         | 串行高级技术附件                |

| SCR          | Smart Card Reader                                             | 智能卡读卡器                  |

| SD Card      | Secure Digital Memory Card                                    | 安全数码卡                   |

| SDIO         | Secure Digital Input and Output Card                          | 安全数字输入输出卡               |

| SDMMC        | Secure Digital Multi Media Card                               | 安全数字多媒体存储卡              |

| SGMII        | Serial Gigabit Media Independent Interface                    | 串行千兆媒体独立接口              |

| SPDIF        | Sony/Philips Digital Interface Format                         | SONY、PHILIPS数字音频接口      |

| SPI          | Serial Peripheral Interface                                   | 串行外设接口                  |

| SubLVDS      | Sub- Low-Voltage Differential Signaling                       | 低摆幅差分信号技术               |

| TF Card      | Micro SD Card(Trans-flash Card)                               | 外置记忆卡                   |

| TSADC        | Temperature sensing A / D converter                           | 温度感应模数转换器               |

| UART         | Universal Asynchronous Receiver / Transmitter                 | 通用异步收发传输器               |

| VOP          | Video Output Processor                                        | 视频输出处理器                 |

| VPU          | Video Processing Unit                                         | 视频处理器                   |

|              | Universal Serial Bus 2.0                                      | 通用电行台建                  |

| USB2.0       | Universal Serial Bus 2.0                                      | 通用串行总线                  |

## Contents

| Contents                                                                                   |      |

|--------------------------------------------------------------------------------------------|------|

| Figures                                                                                    | VIII |

| Tables                                                                                     | XV   |

| 1 System Introduction                                                                      |      |

| 1.1 Overview                                                                               |      |

| 1.2 Block Diagram                                                                          |      |

| 1.3 Application Block Diagram                                                              |      |

| 1.3.1 RK3568 EVB Application Block Diagram                                                 |      |

| 1.3.2 RK3568 Smart NVR Application Block Diagram                                           |      |

| 1.3.2 RK3568 Smart NVR Application Block Diagram         2 Schematic Design Recommendation |      |

| 2.1 Minimum System Design                                                                  |      |

| 2.1.1 Clock Circuit                                                                        |      |

| 2.1.2 Reset/watchdog/TSADC Circuit                                                         | 6    |

| 2.1.3 PMU Circuit                                                                          |      |

| 2.1.4 System Boot Sequence                                                                 |      |

| 2.1.5 System Initialization Configuration Signal                                           |      |

| 2.1.6 JTAG and UART Debug Circuit                                                          |      |

| 2.1.7 DDR Circuit                                                                          |      |

| 2.1.8 eMMC Circuit                                                                         |      |

| 2.1.9 FSPI Flash Circuit                                                                   |      |

| 2.1.10 Nand Flash Circuit                                                                  |      |

| 2.1.11 GPIO Circuit                                                                        |      |

| 2.2 Power Supply Design                                                                    |      |

| 2.2.1 RK3568 Power Supply Introduction                                                     |      |

| 2.2.2 Power Supply Design Suggestion                                                       |      |

| 2.2.3 RK809-5 Solution Introduction                                                        |      |

| 2.2.4 Discrete Power Supply Solution Introduction                                          | 59   |

| 2.2.5 Standby Control Circuit                                                              |      |

| 2.2.6 Power Peak Current Table                                                             |      |

| 2.3 Functional Interface Circuit Design Guide                                              |      |

| 2.3.1 SDMMC0/1/2                                                                           |      |

| 2.3.2 SARADC Circuit                                                                       | 69   |

| 2.3.3 OTP Circuit                                                                          |      |

| 2.3.4 USB2.0/USB3.0 Circuit                                                                |      |

| 2.3.5 SATA3.0 Circuit                                                                      |      |

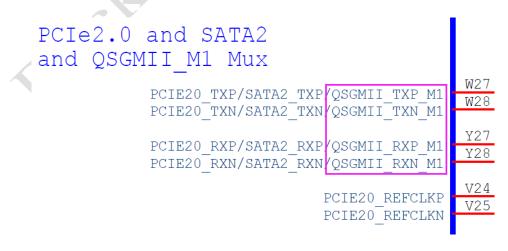

| 2.3.6 QSGMII/SGMII Circuit                                                                 |      |

| 2.3.7 PCIe2.0 Circuit                                                                      |      |

| 2.3.8 PCIe3.0 Circuit                                                                      |      |

| Copyright © 2022 Rockchip Electronics Co., Ltd.                                            | V    |

| RK3568 Hardware Design Guide                     | <i>Rev V1.2</i> |

|--------------------------------------------------|-----------------|

| 2.3.9 Video Input Interface Circuit              |                 |

| 2.3.10 Video Output Interface Circuit            |                 |

| 2.3.11 Audio Interface Circuit                   | 118             |

| 2.3.12 GMAC Interface Circuit                    | 137             |

| 2.3.13 UART Interface Circuit                    | 144             |

| 2.3.14 SPI Interface Circuit                     | 146             |

| 2.3.15 CAN Interface Circuit                     | 146             |

| 2.3.16 I2C Interface Circuit                     | 147             |

| 2.3.17 PWM Interface Circuit                     | 148             |

| 2.3.18 RK3568 Unused Modules Pins Processing     | 150             |

| 3 PCB Design recommendations                     |                 |

| 3.1 PCB Layers Design                            |                 |

| 3.1.1 Six Layers PCB Design                      |                 |

| 3.1.2 Four Layers PCB Design                     | 152             |

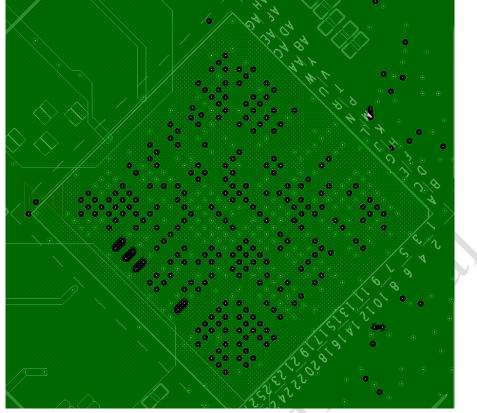

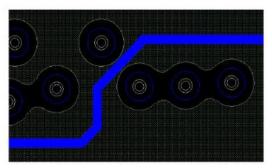

| 3.1.3 RK3568 Fan-out Design                      |                 |

| 3.2 Interface PCB Design Recommendations         |                 |

| 3.2.1 Clock/Reset Circuit PCB Design             |                 |

| 3.2.2 PMIC/Power Circuit PCB Design              | 158             |

| 3.2.3 DRAM Circuit PCB design                    |                 |

| 3.2.4 Flash Circuit PCB design                   |                 |

| 3.2.5 SDMMC0/1/2 Interface Crcuit PCB Design     | 199             |

| 3.2.6 SARADC/OTP Interface Circuit PCB Design    | 200             |

| 3.2.7 USB2.0 Interface Circuit PCB Design        | 200             |

| 3.2.8 USB3.0 Interface Circuit PCB Design        | 201             |

| 3.2.9 SATA3.0 Interface Circuit PCB Design       | 202             |

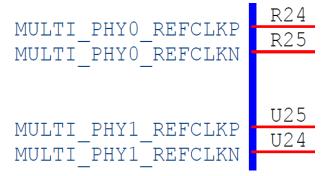

| 3.2.10 QSGMII/SGMII Interface Circuit PCB Design | 203             |

| 3.2.11 PCIe2.0 Interface Circuit PCB Design      | 204             |

| 3.2.12 PCIe3.0 Interface Crcuit PCB Design       | 206             |

| 3.2.13 MIPI CSI RX Interface Circuit PCB Design  | 207             |

| 3.2.14 CIF Interface Circuit PCB Design          | 208             |

| 3.2.15 MIPI DSI TX Interface Circuit PCB Design  | 208             |

| 3.2.16 LVDS TX Interface Circuit PCB Design      | 209             |

| 3.2.17 eDP TX Interface Circuit PCB Design       | 210             |

| 3.2.18 HDMI TX Interface Circuit PCB Design      | 210             |

| 3.2.19 RGB TX Interface Circuit PCB Design       | 211             |

| 3.2.20 BT1120 TX Interface Circuit PCB Design    | 212             |

| 3.2.21 Audio Interface Circuit PCB Design        | 213             |

| 3.2.22 GMAC Interface Circuit PCB Design         | 214             |

| 3.2.23 WIFI/BT PCB Design                        | 218             |

| 3.2.24 VGA OUT PCB Design                        | 219             |

| Committee 2022 Deschables Florenzaise Constant   | 171             |

| RK3568 Hardware Design Guide                     | <i>Rev V1.2</i> |

|--------------------------------------------------|-----------------|

| 3.2.25 LCD Screen and Touch Screen PCB Design    |                 |

| 3.2.26 Camera PCB Design                         |                 |

| 4 Thermal Design Suggestion                      |                 |

| 4.1 Thermal Simulation Result                    |                 |

| 4.1.1 Result Overview                            |                 |

| 4.1.2 PCB Description                            |                 |

| 4.1.3 Terms Interpretation                       |                 |

| 4.2 Thermal Control Method inside the Chip       |                 |

| 4.2.1 Thermal Control Strategy                   |                 |

| 4.2.2 Temperature Control Configuration          |                 |

| 4.3 Thermal Design Reference                     |                 |

| 4.3.1 Circuit Schematic Thermal Design Reference |                 |

| 4.3.2 PCB Thermal Design Reference               |                 |

| 5 ESD/EMI Protection Design                      |                 |

| 5.1 Overview                                     |                 |

| 5.2 Terms Interpretation                         |                 |

| 5.3 ESD Protection                               |                 |

| 5.4 EMI Protection                               |                 |

| 6 Soldering Process                              |                 |

| 6.1 Overview                                     |                 |

| 6.2 Terms Interpretation                         |                 |

| 6.3 Reflow Soldering Requirements                |                 |

| 6.3.1 Solder Paste Composition Requirements      |                 |

| 6.3.2 SMT Profile                                |                 |

| 6.3.3 SMT Recommendation Profile                 |                 |

| 7 Packages and Storage Conditions                |                 |

| 7.1 Overview                                     |                 |

| 7.2 Terms Interpretation                         |                 |

| 7.3 Moisture Packages                            |                 |

| 7.4 Product Storage                              |                 |

| 7.4.1 Storage Environment                        |                 |

| 7.4.2 Exposure Time                              |                 |

| 7.5 Usage of Moisture Sensitive Products         |                 |

# Figures

| Figure 1-1 RK3568 block diagram                                       | 1  |

|-----------------------------------------------------------------------|----|

| Figure 1-2 RK3568 EVB application block diagram                       | 2  |

| Figure 1-3 RK3568 Smart NVR application block diagram                 | 3  |

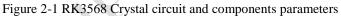

| Figure 2-1 RK3568 Crystal circuit and components parameters           | 4  |

| Figure 2-2 RK3568 the 32.768KHz clock input pin in standby            | 5  |

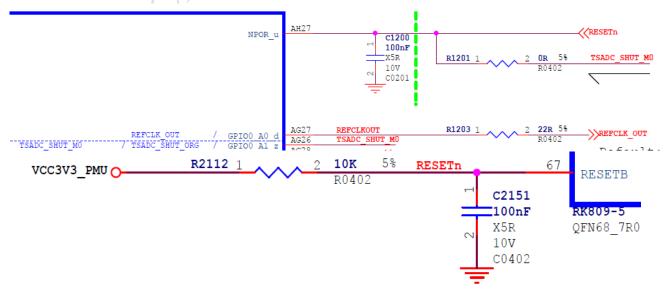

| Figure 2-3 RK3568 reset input (RK809-5 solution)                      | 6  |

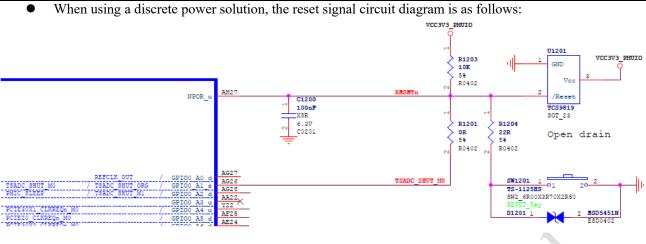

| Figure 2-4 RK3568 reset input (discrete power solution)               | 7  |

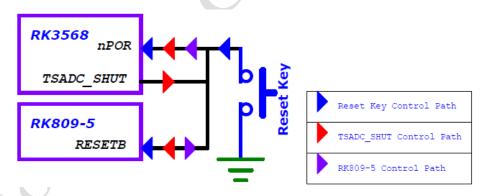

| Figure 2-5 RK3568 the path of reset signal                            | 7  |

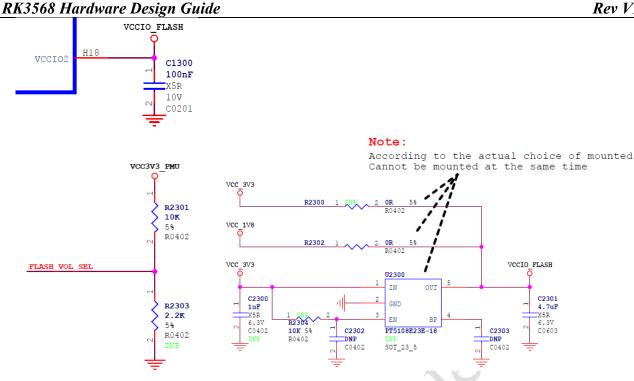

| Figure 2-6 RK3568 VCCIO2 power supply and FLASH_VOL_SEL               | 9  |

| Figure 2-7 RK3568 SDMMC0/ARM JTAG multiplexed pins and SDMMC0 DET pin | 9  |

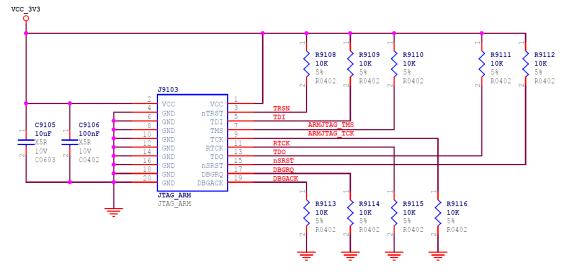

| Figure 2-8 RK3568 JTAG connection schematic                           | 10 |

| Figure 2-9 RK3568 ARM JTAG pin                                        | 11 |

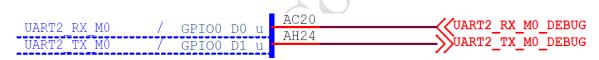

| Figure 2-10 RK3568 UART2 M0 pin                                       | 11 |

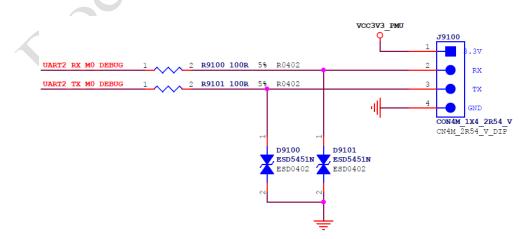

| Figure 2-11 RK3568 Debug UART2 Connection diagram                     | 11 |

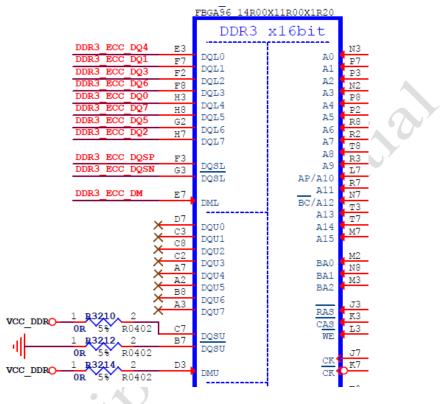

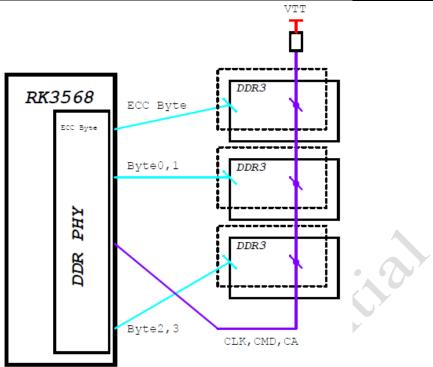

| Figure 2-12 RK3568 16bit ECC DDR3/DDR3L processing method             | 15 |

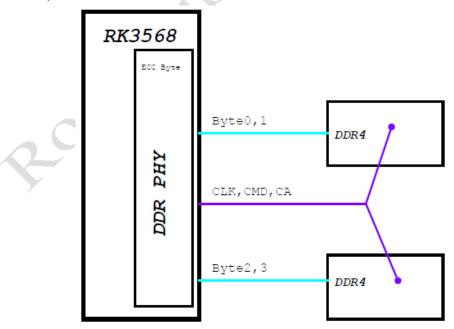

| Figure 2-13 RK3568 16bit ECC DDR4 processing method                   | 15 |

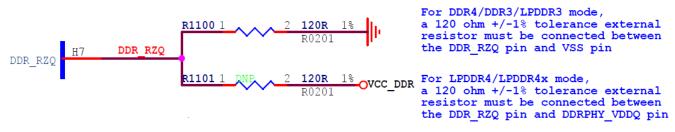

| Figure 2-14 RK3568 DDR_RZQ pin                                        | 16 |

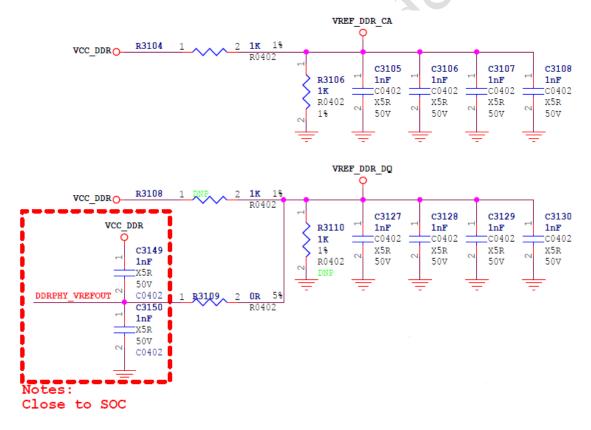

| Figure 2-15 DDR3/DDR3L VREF circuit                                   | 16 |

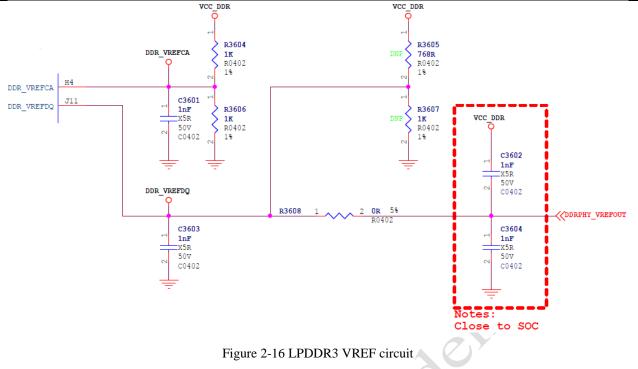

| Figure 2-15 DDR3/DDR3L VREF circuit                                   | 17 |

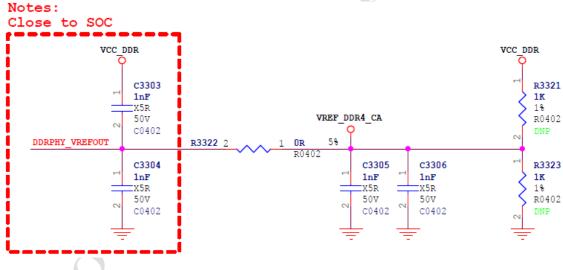

| Figure 2-17 DDR4 VREF circuit                                         | 17 |

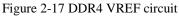

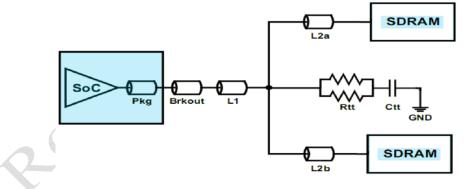

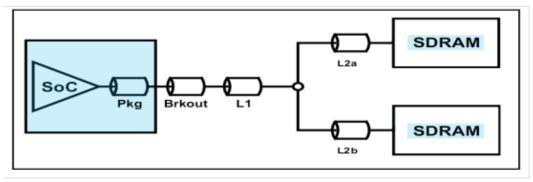

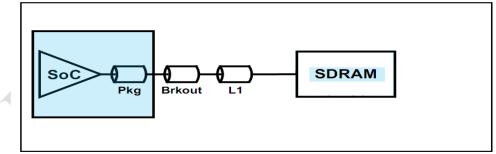

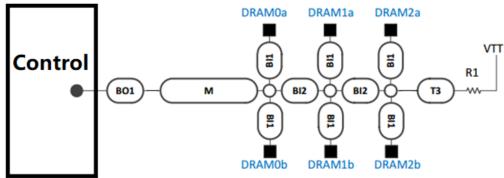

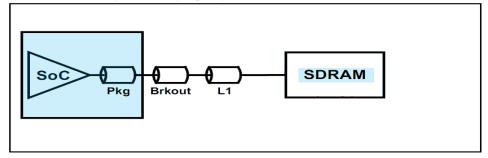

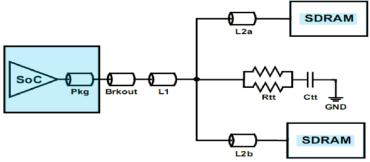

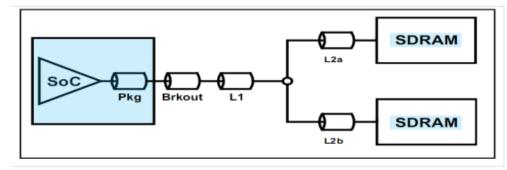

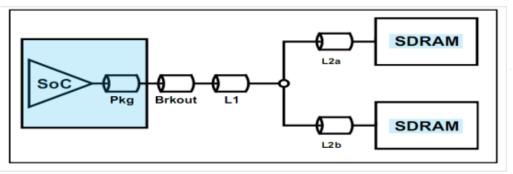

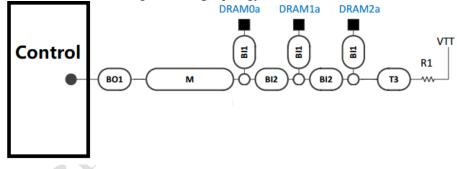

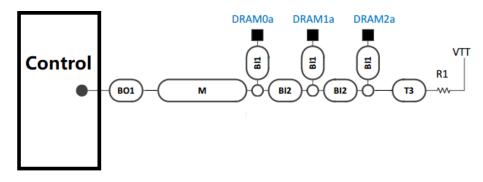

| Figure 2-18 DDR3/DDR3L T topology                                     | 18 |

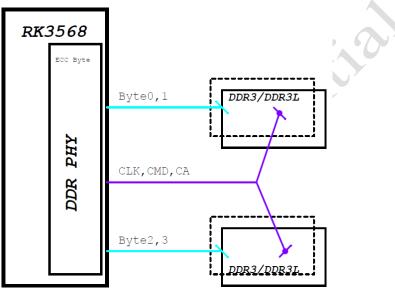

| Figure 2-19 The CLKP/CLKN termination of DDR3/DDR3L T topology        |    |

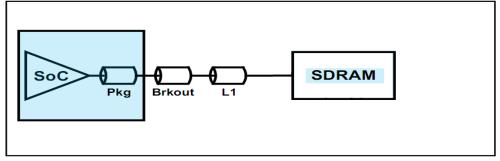

| Figure 2-20 DDR3/DDR3L Fly-by topology                                | 19 |

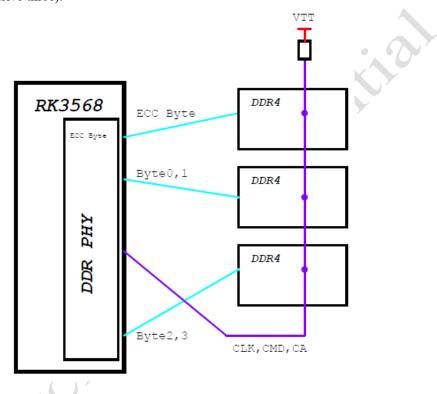

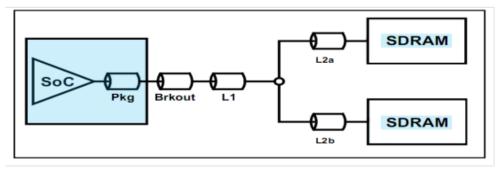

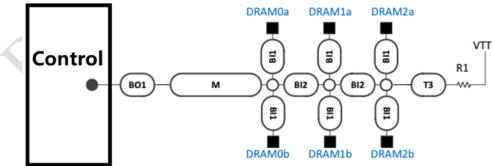

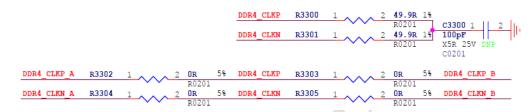

| Figure 2-21 DDR4 T topology                                           | 19 |

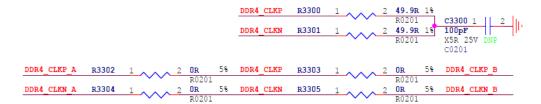

| Figure 2-22 The CLKP/CLKN termination of DDR4 T topology              |    |

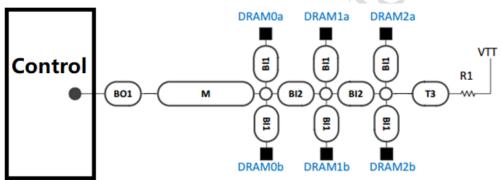

| Figure 2-23 DDR4 Fly-by topology                                      | 20 |

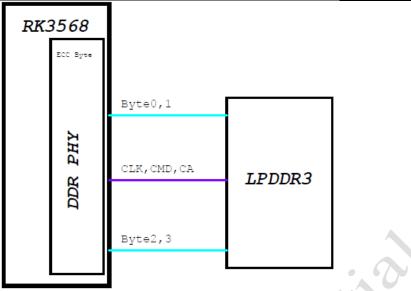

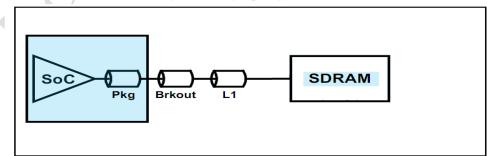

| Figure 2-24 LPDDR3 point-to-point topology                            | 21 |

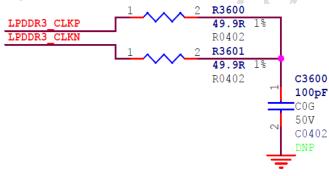

| Figure 2-25 LPDDR3 CLKP/CLKN termination                              | 21 |

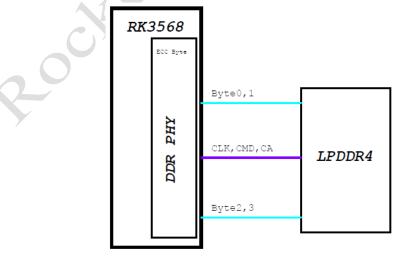

| Figure 2-26 LPDDR4 point-to-point topology                            | 21 |

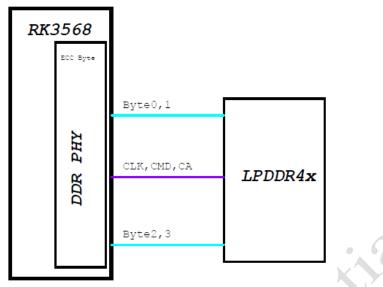

| Figure 2-27 LPDDR4X point-to-point topology                           | 22 |

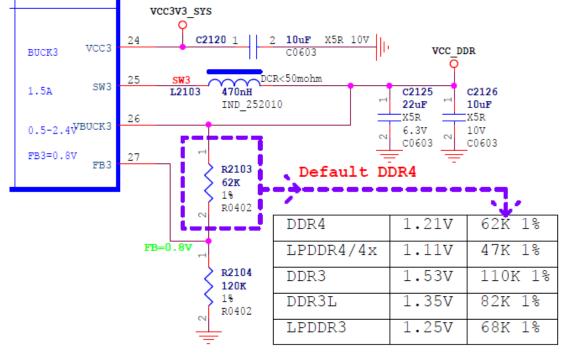

| Figure 2-28 RK809-5 BUCK3 parameters regulation                       | 23 |

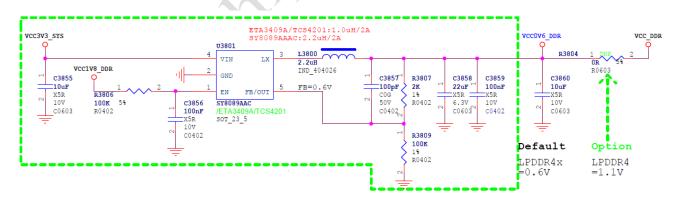

| Figure 2-29 Power selection of LPDDR4/LPDDR4x compatible design       | 23 |

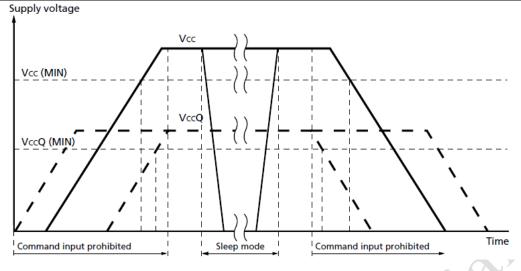

| Figure 2-30 DDR3 SDRAM power up sequence                              | 24 |

| Figure 2-31 LPDDR3 SDRAM power up sequence                            | 24 |

| Figure 2-32 DDR4 SDRAM power up sequence                              | 24 |

| Figure 2-33 LPDDR4/4x SDRAM power up sequence                         | 25 |

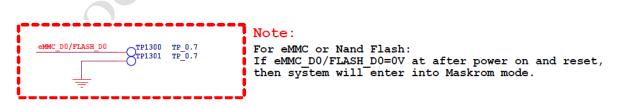

| Figure 2-34 eMMC_D0 test point                                        | 26 |

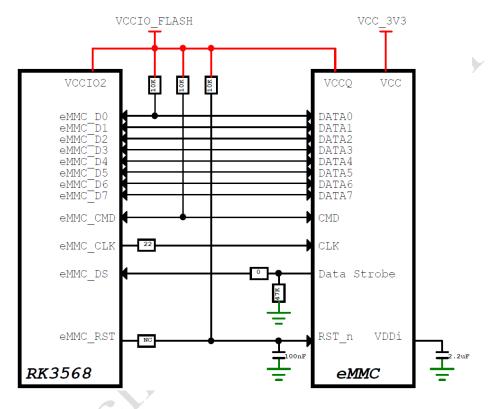

| Figure 2-35 eMMC connection diagram                                   | 26 |

| RK3568 Hardware Design Guide                                               | <i>Rev V1.2</i> |

|----------------------------------------------------------------------------|-----------------|

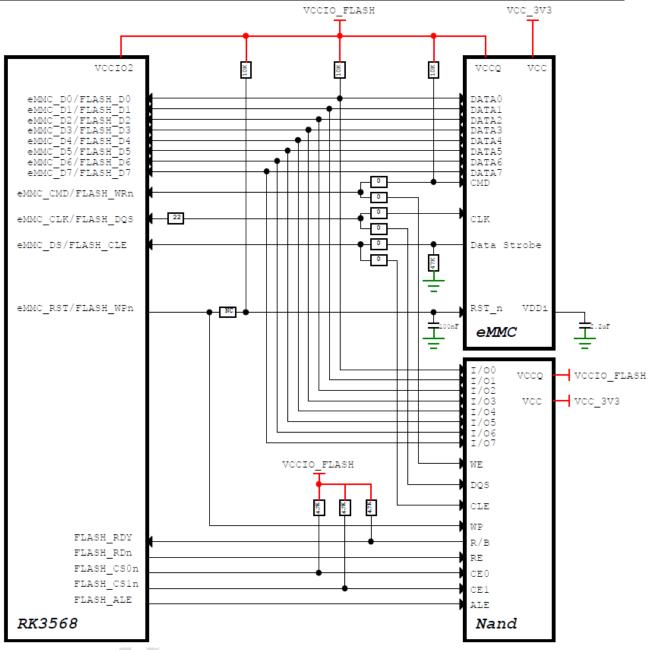

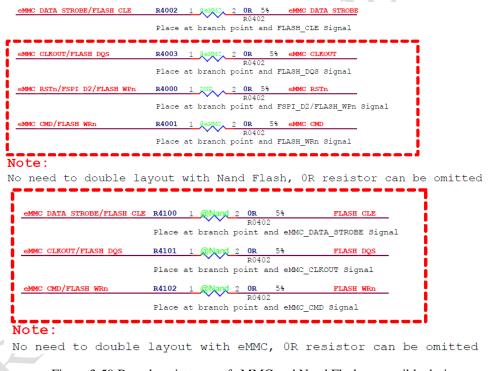

| Figure 2-36 Connection diagram of eMMC and Nand Flash in compatible design | 27              |

| Figure 2-37 eMMC power up and power down sequence                          |                 |

| Figure 2-38 FSPI_CLK test point                                            | 29              |

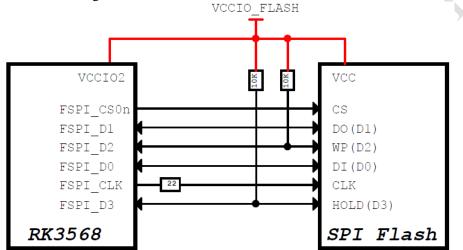

| Figure 2-39 FSPI Flash connection diagram                                  | 29              |

| Figure 2-40 Flash_D0 test point                                            |                 |

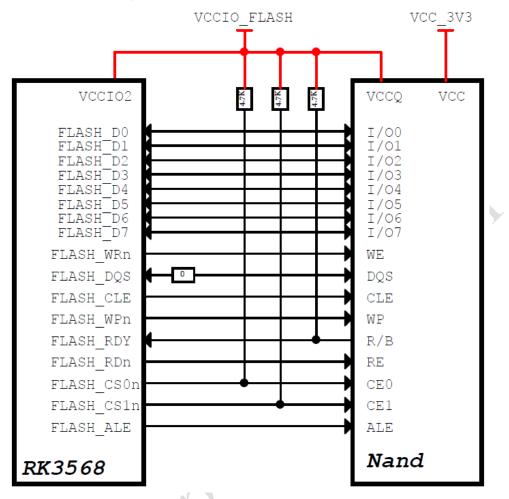

| Figure 2-41 Nand Flash connection diagram                                  |                 |

| Figure 2-42 Nand Flash power up and down sequence                          |                 |

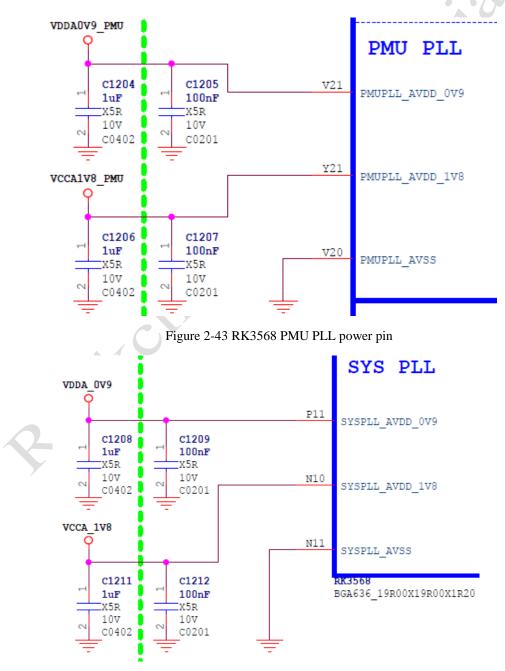

| Figure 2-43 RK3568 PMU PLL power pin                                       | 40              |

| Figure 2-44 RK3568 SYS PLL power pin                                       | 40              |

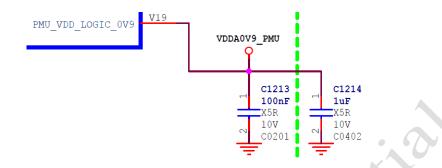

| Figure 2-45 RK3568 PMU_VDD_LOGIC_0V9 power pin                             | 41              |

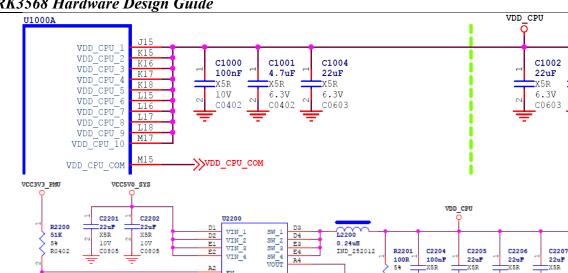

| Figure 2-46 RK3568 VDD_CPU power pin and power supply DC/DC                |                 |

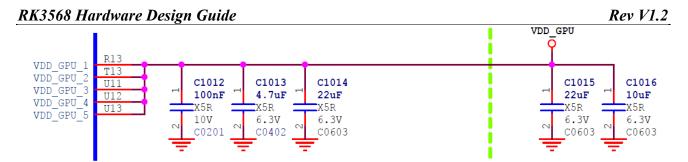

| Figure 2-47 RK3568 VDD_GPU power pin                                       | 43              |

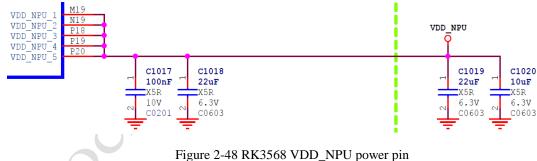

| Figure 2-48 RK3568 VDD_NPU power pin                                       | 43              |

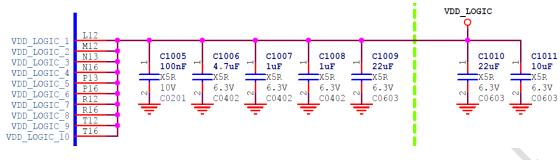

| Figure 2-49 RK3568 VDD_LOGIC power pin                                     | 44              |

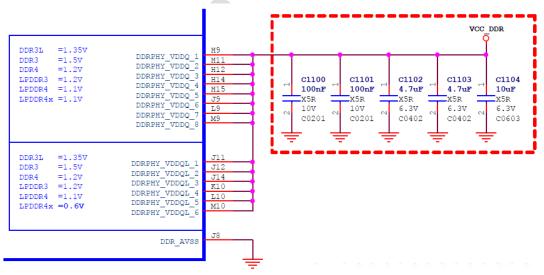

| Figure 2-50 RK3568 VCC_DDR power pin in DDR3/DDR3L/DDR4/LPDDR3/LPDDR4 mode | 44              |

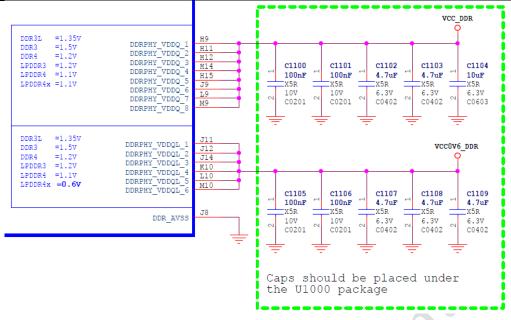

| Figure 2-51 RK3568 VCC_DDR and VCC0V6_DDR power pins in LPDDR4x mode       | 45              |

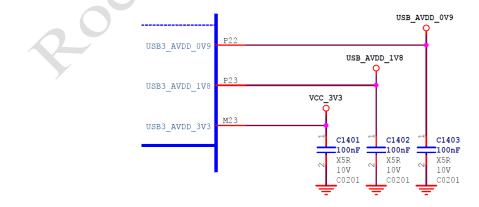

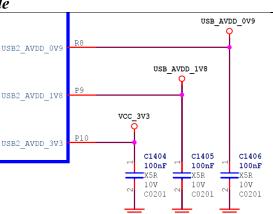

| Figure 2-52 RK3568 USB2.0 PHY power pin                                    | 46              |

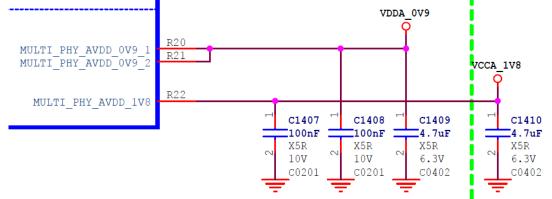

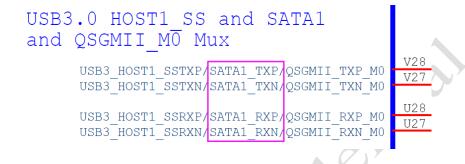

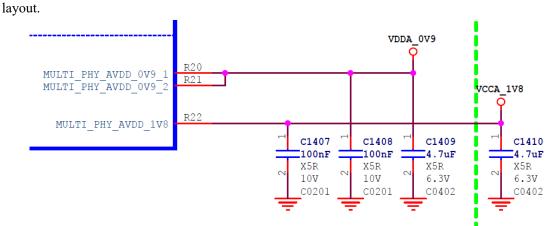

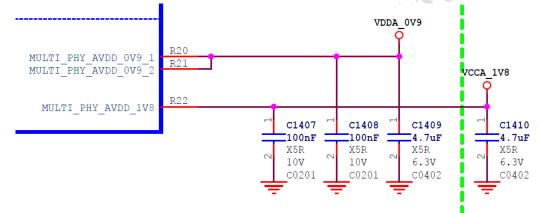

| Figure 2-53 RK3568 MULTI_PHY power pin                                     | 47              |

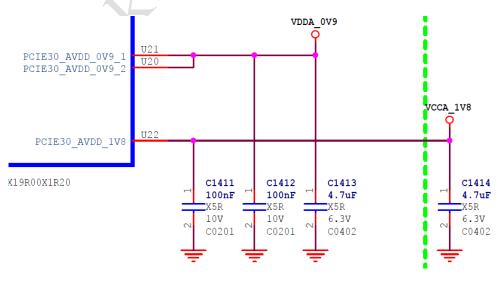

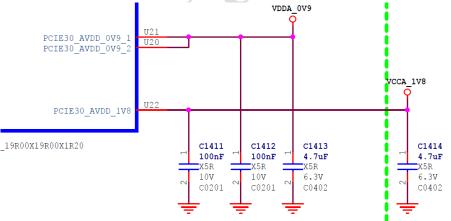

| Figure 2-54 RK3568 PCIe3.0 PHY power pin                                   | 47              |

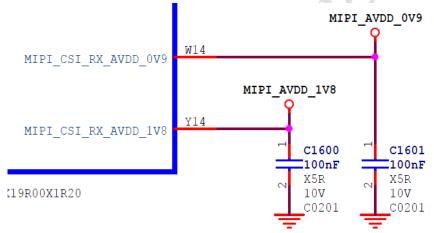

| Figure 2-55 RK3568 MIPI CSI RX PHY power pin                               | 48              |

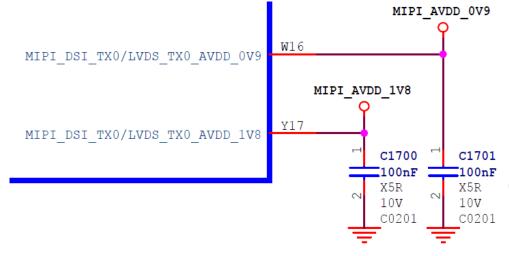

| Figure 2-56 RK3568 MIPI DSI TX0 and LVDS TX Combo PHY power pin            | 49              |

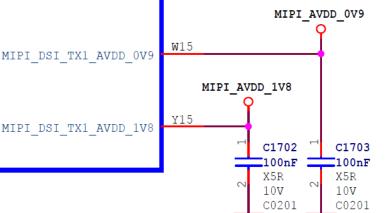

| Figure 2-57 RK3568 MIPI DSI TX1 PHY power pin                              | 50              |

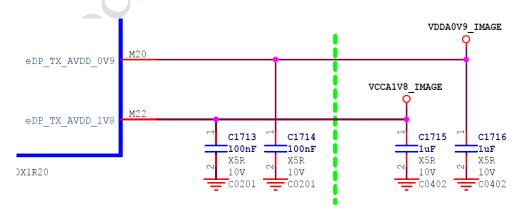

| Figure 2-58 RK3568 eDP TX PHY power pin                                    | 50              |

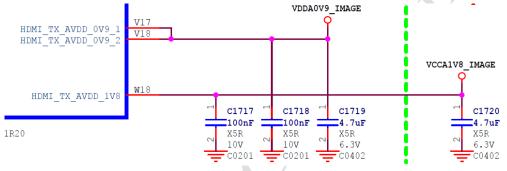

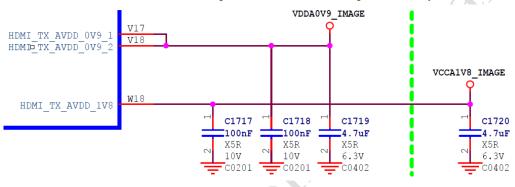

| Figure 2-59 RK3568 HDMI2.0 TX PHY power pin                                | 51              |

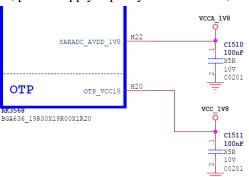

| Figure 2-60 RK3568 SARADC and OTP power pin                                |                 |

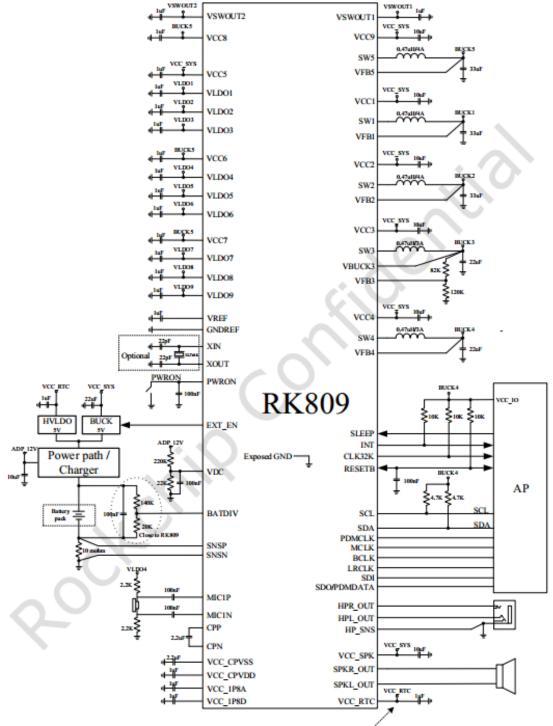

| Figure 2-61 RK809-5 block diagram                                          | 53              |

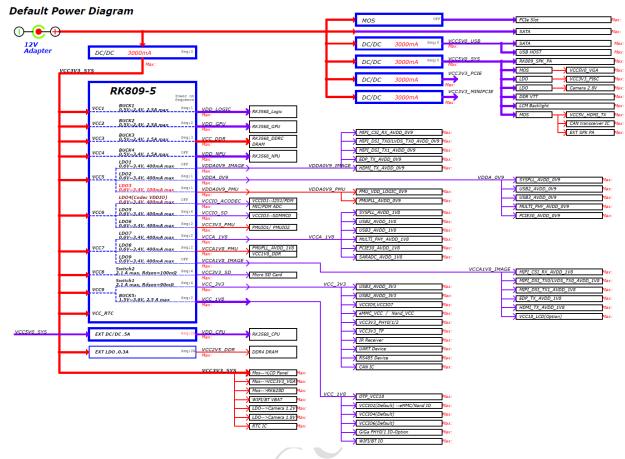

| Figure 2-62 RK3568 and RK809-5 power tree                                  | 55              |

| Figure 2-63 RK809-5 power-on sequence                                      | 56              |

| Figure 2-64 RK3568 + discrete power architecture                           | 59              |

| Figure 2-65 Discrete power-on sequence                                     | 60              |

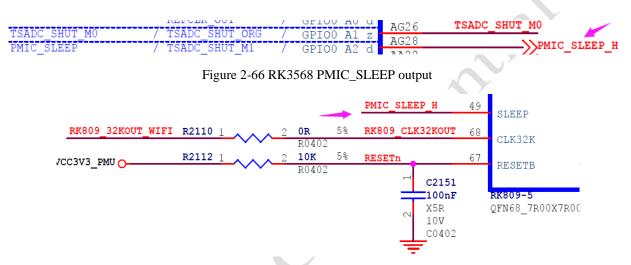

| Figure 2-66 RK3568 PMIC_SLEEP output                                       | 62              |

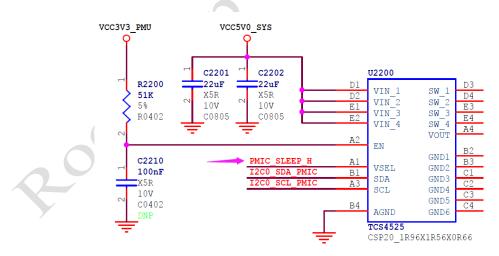

| Figure 2-67 RK809-5 PMIC_SLEEP input                                       | 62              |

| Figure 2-68 The PMIC_SLEEP input of VDD_CPU BUCK                           | 62              |

| Figure 2-69 RK3568 SDMMC0 interface pin                                    | 64              |

| Figure 2-70 SD card interface circuit                                      | 65              |

| Figure 2-71 RK3568 SDMMC1 interface pin                                    | 66              |

| Figure 2-72 RK3568 SDMMC2 interface M0 functional pins                     | 67              |

| Figure 2-73 RK3568 SDMMC2 interface M1 functional pins                     | 68              |

| Figure 2-74 SARADC VIN0 interface                                          | 69              |

| Figure 2-75 RK3568 SARADC module                                           | 70              |

| Copyright © 2022 Rockchip Electronics Co., Ltd.                            | IX              |

| RK3568 Hardware Design Guide                                                                    | <i>Rev V1.2</i> |

|-------------------------------------------------------------------------------------------------|-----------------|

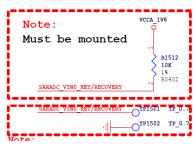

| Figure 2-76 The button circuit using SARADC sampling                                            | 70              |

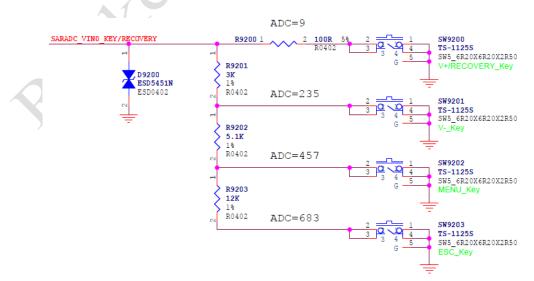

| Figure 2-77 RK3568 OTP power pin                                                                | 71              |

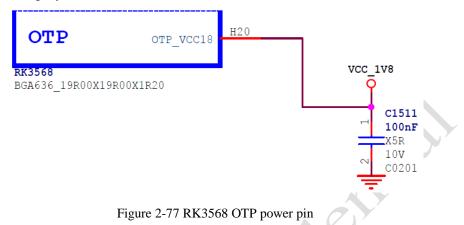

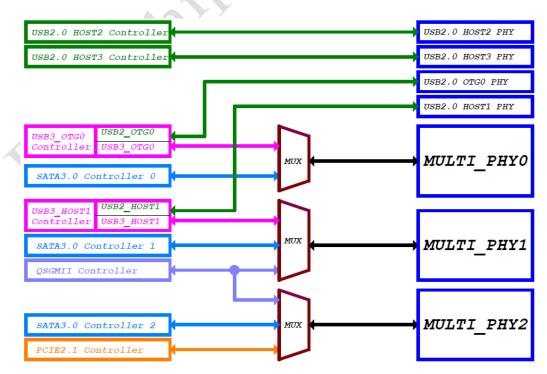

| Figure 2-78 Multiplexing relationship between MULTI_PHY0/1and USB3.0 controllers                | 71              |

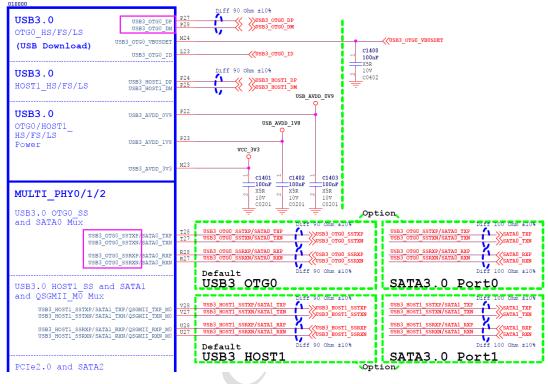

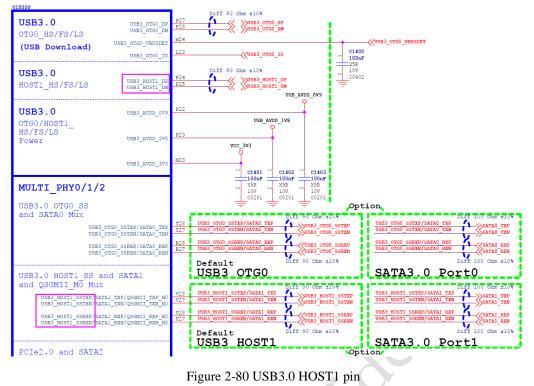

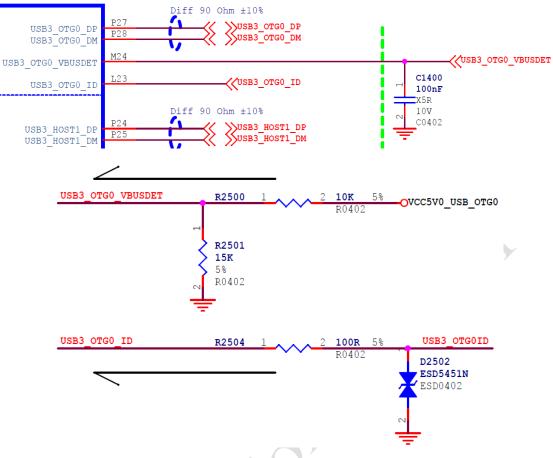

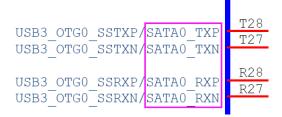

| Figure 2-79 USB3.0 OTG0 pin                                                                     | 72              |

| Figure 2-80 USB3.0 HOST1 pin                                                                    | 73              |

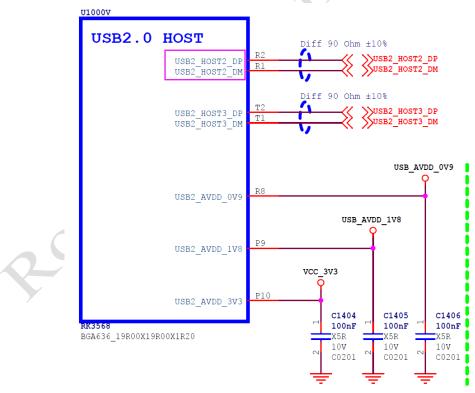

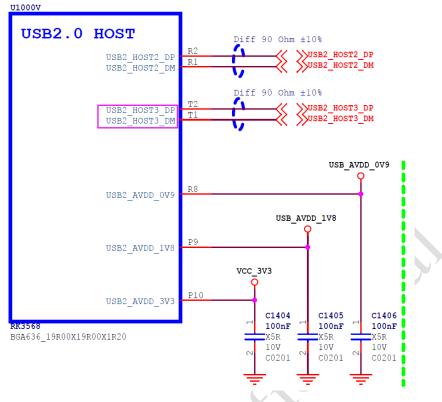

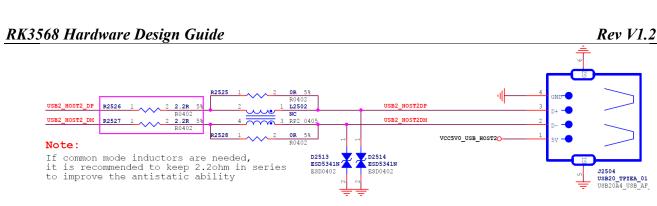

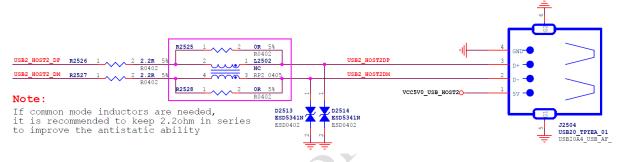

| Figure 2-81 USB2.0 HOST2 pin                                                                    | 73              |

| Figure 2-82 USB2.0 HOST3 pin                                                                    | 74              |

| Figure 2-83 RK3568 VBUSDET and ID Circuit                                                       | 75              |

| Figure 2-84 USB2.0 PHY power supply magnetic bead isolation circuit                             | 75              |

| Figure 2-85 USB2.0 signal is connected in series with a 2.20hm resistor                         | 76              |

| Figure 2-86 USB2.0 signal is connected in series with common mode choke circuit                 | 76              |

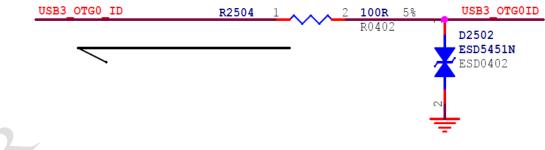

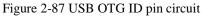

| Figure 2-87 USB OTG ID pin circuit                                                              | 76              |

| Figure 2-88 USB 5V current-limiting circuit.                                                    | 77              |

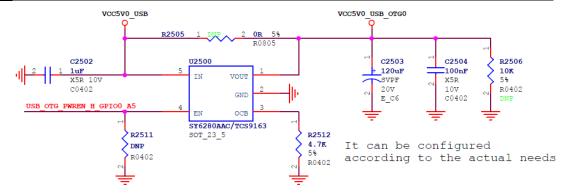

| Figure 2-89 USB3.0 ESD circuit                                                                  | 77              |

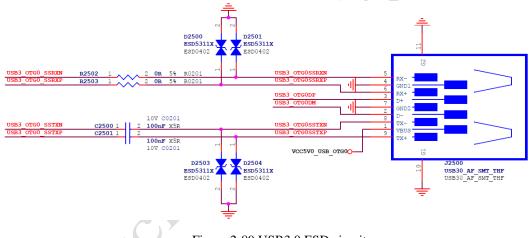

| Figure 2-90 MULTI PHY power supply decoupling circuit                                           | 77              |

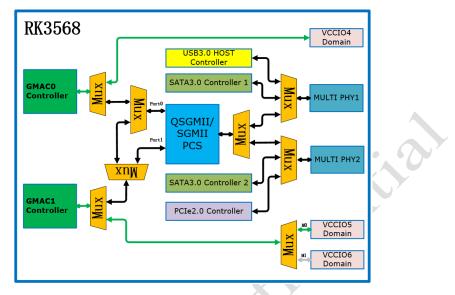

| Figure 2-91 MULTI_PHY0/1/2 and SATA3.0 controller multiplexing relationship                     | 78              |

| Figure 2-92 SATA0/1/2 related control IO pins                                                   |                 |

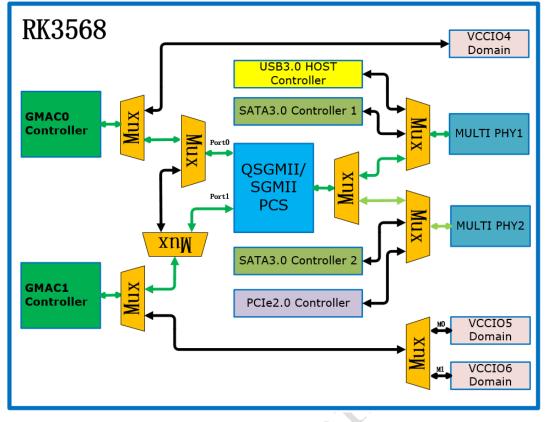

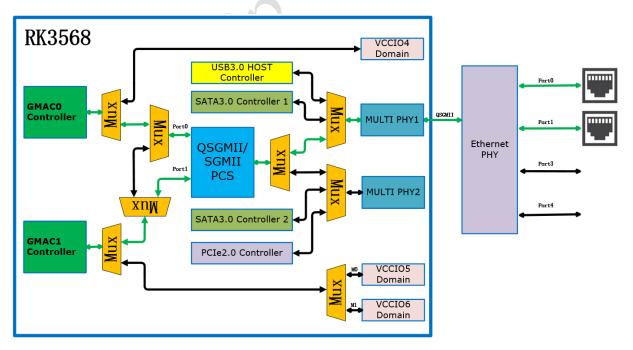

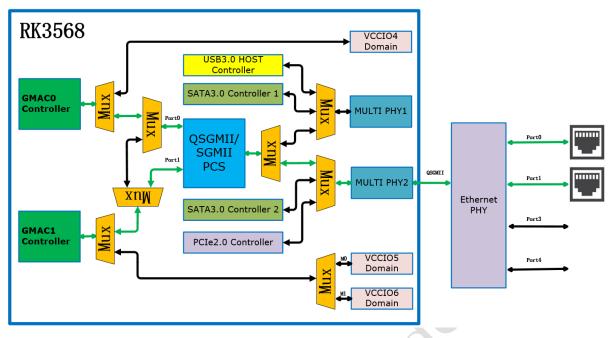

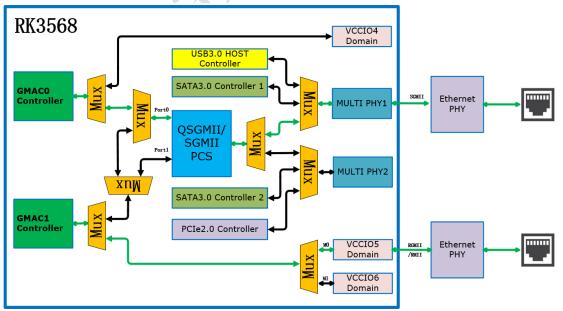

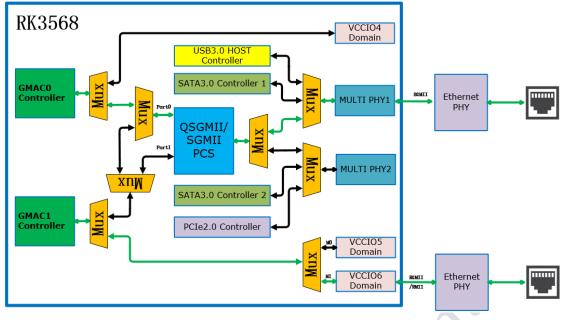

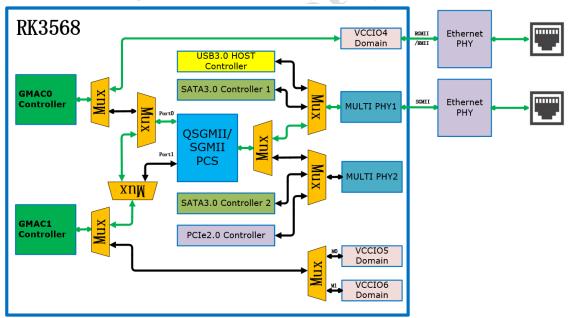

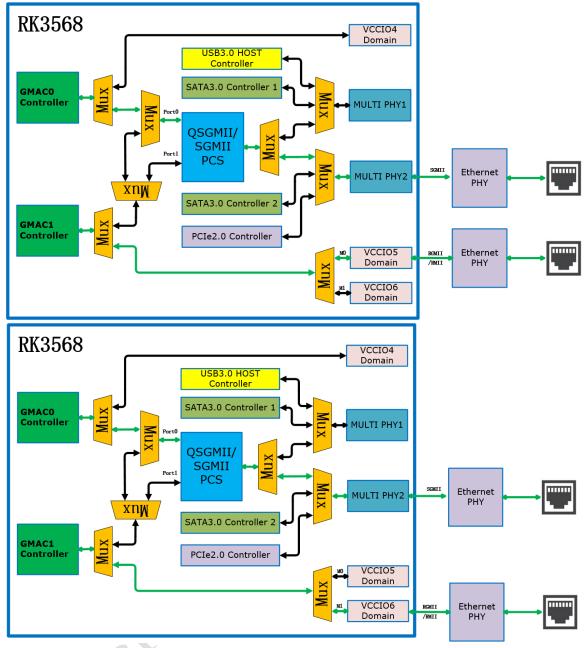

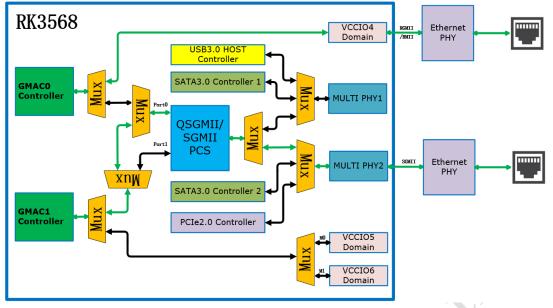

| Figure 2-93 The paths of GMAC0, GMAC1, QSGMII/SGMII PCS and QSGMII/SGMII PHY                    |                 |

| Figure 2-94 The application block diagram of QSGMII-MULTI_PHY1Y1                                |                 |

| Figure 2-95 The application block diagram of QSGMII-MULTI_PHY2                                  |                 |

| Figure 2-96 The application block diagram of GMAC0-SGMII-MULTI_PHY1                             |                 |

| Figure 2-97 The application block diagram of GMAC1-SGMII-MULTI_PHY1                             |                 |

| Figure 2-98 The application block diagram of GMAC0-SGMII-MULTI_PHY2                             |                 |

| Figure 2-99 The application block diagram of GMAC1-SGMII-MULTI_PHY2                             |                 |

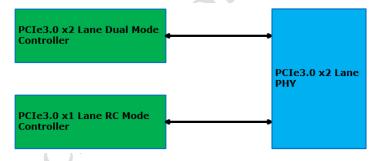

| Figure 2-100 PCIe3.0 controller/PCIe3.0 PHY block diagram                                       |                 |

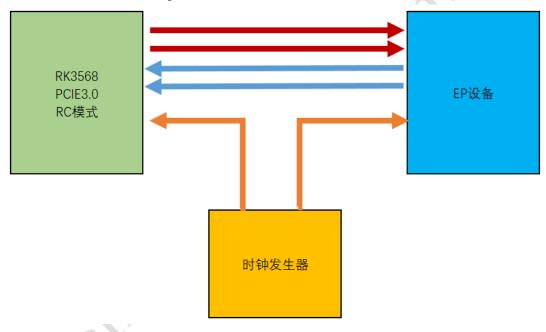

| Figure 2-101 Reference clock paths in RK3568 PCIe3.0 x2 Lane RC mode                            | 90              |

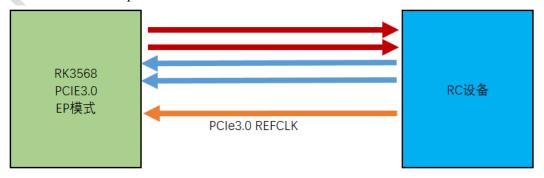

| Figure 2-102 Reference clock paths in RK3568 PCIe3.0 x2 Lane EP mode                            | 90              |

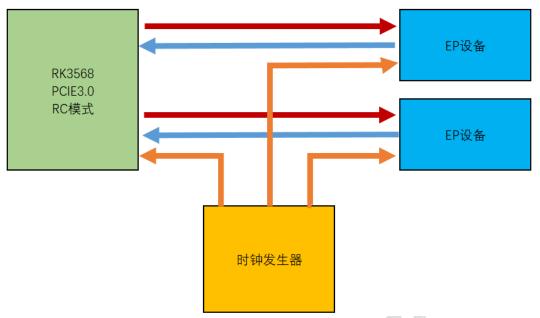

| Figure 2-103 The reference clock paths in RK3568 PCIe3.0 x1 Lane RC mode + PCIe3.0 x1 Lane RC n | 10de91          |

| Figure 2-104 PCIe3.0 PHY power decoupling capacitors                                            | 91              |

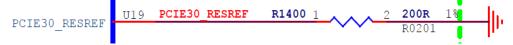

| Figure 2-105 PCIe3.0 PHY RESREF pin                                                             | 91              |

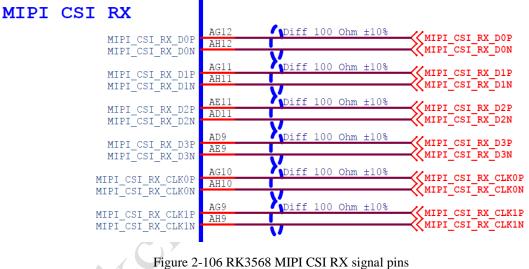

| Figure 2-106 RK3568 MIPI CSI RX signal pins                                                     | 93              |

| Figure 2-107 RK3568 MIPI CSI working mode and data, clock allocation                            | 94              |

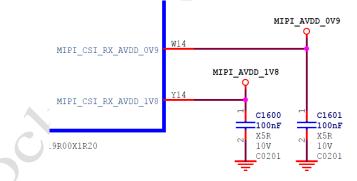

| Figure 2-108 MIPI CSI PHY power circuit isolated with magnetic beads                            | 94              |

| Figure 2-109 MIPI CSI RX PHY power decoupling capacitors                                        | 94              |

| Figure 2-110 RK3568 CIF functional pins                                                         | 95              |

| Figure 2-111 RK3568 Relationship between data of CIF                                            | 96              |

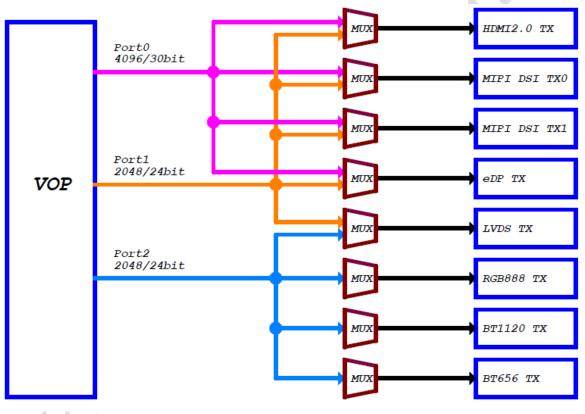

| Figure 2-112 RK3568 the output path diagram of VOP and video interface                          | 98              |

| Figure 2-113 RK3568 HDMI2.0 TX PHY TMDS pins                                                    | 99              |

| Figure 2-114 RK3568 HDMI2.0 TX PHY power supply decoupling capacitances                         | 99              |

| Figure 2-115 RK3568 HDMI2.0 TX PHY REXT pins                                                    | 99              |

| Copyright © 2022 Rockchip Electronics Co., Ltd.                                                 | Х               |

| RK3568 Hardware Design Guide                                                    | <i>Rev V1.2</i> |

|---------------------------------------------------------------------------------|-----------------|

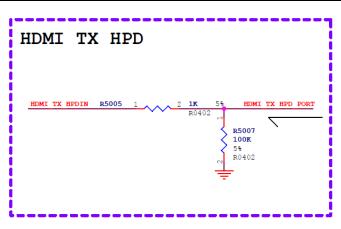

| Figure 2-116 RK3568 HDMI2.0 TX PHY HPD pins                                     |                 |

| Figure 2-117 RK3568 HDMI2.0 TX PHY HPD circuit                                  | 100             |

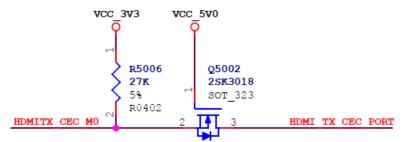

| Figure 2-118 HDMI CEC protocol requirements                                     | 100             |

| Figure 2-119 HDMI CEC CEC isolating circuit                                     | 100             |

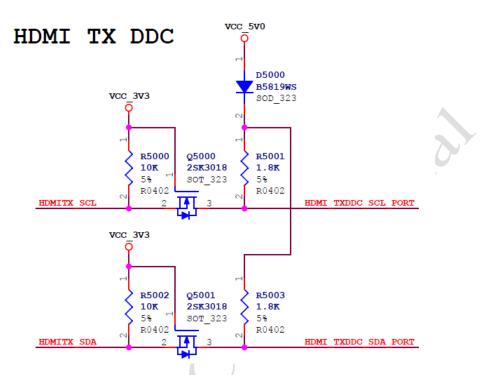

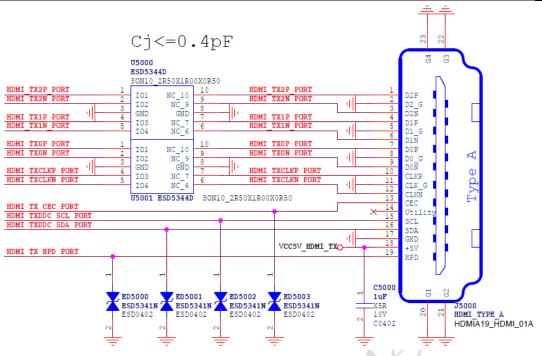

| Figure 2-120 HDMI DDC level conversion circuit                                  | 101             |

| Figure 2-121 ESD circuit of HDMI connector                                      |                 |

| Figure 2-122 RK3568 MIPI DSI TX0/LVDS TX Combo PHY pins                         |                 |

| Figure 2-123 Magnetic bead isolation circuit of MIPI DSI PHY power supply       |                 |

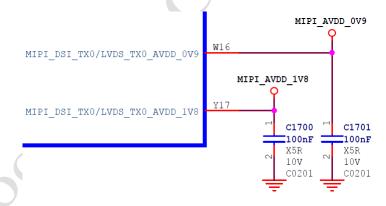

| Figure 2-124 RK3568 MIPI DSI TX0/LVDS TX Combo PHY power decoupling capacitors  |                 |

| Figure 2-125 RK3568 MIPI DSI TX1 PHY pins                                       | 104             |

| Figure 2-126 Magnetic bead isolation circuit of MIPI DSI TX1 PHY power supply   |                 |

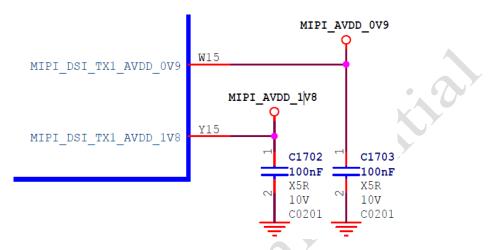

| Figure 2-127 RK3568 MIPI DSI TX1 PHY power decoupling capacitors                |                 |

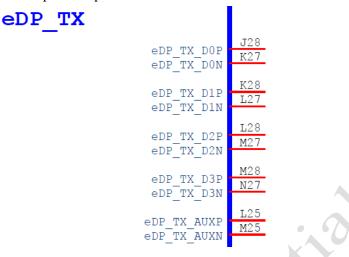

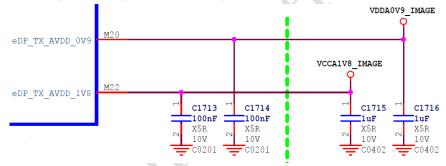

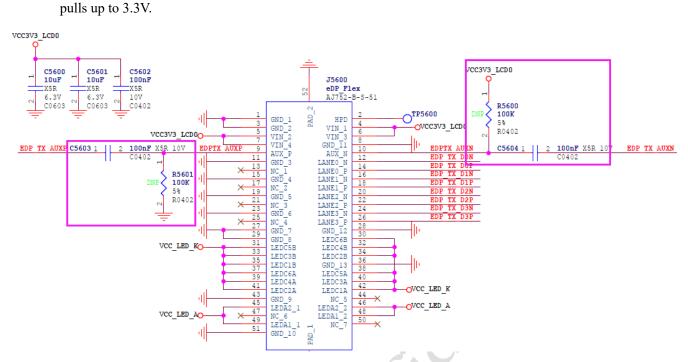

| Figure 2-128 RK3568 eDP TX PHY pins.                                            |                 |

| Figure 2-129 Figure 2–129 RK3568 eDP TX PHY power decoupling capacitors         |                 |

| Figure 2-130 RK3568 eDP TX signal AC decoupling capacitors                      |                 |

| Figure 2-131 RK3568 eDP AUX signal AC decoupling capacitors                     | 107             |

| Figure 2-132 RK3568 LCDC functional pins.                                       |                 |

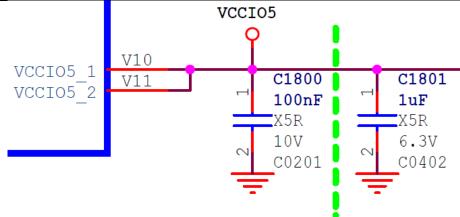

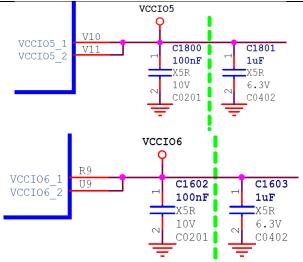

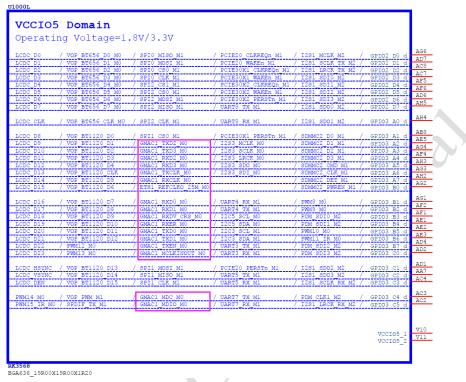

| Figure 2-133 The decoupling capacitors of RK3568 VCCIO5 power supply            | 110             |

| Figure 2-134 RK3568 VOP BT1120 functional pins                                  |                 |

| Figure 2-135 RK3568 VOP BT656 M0 functional pins                                |                 |

| Figure 2-136 RK3568 VOP BT656 M1 functional pins                                | 114             |

| Figure 2-137 RK3568 EBC functional pins                                         | 116             |

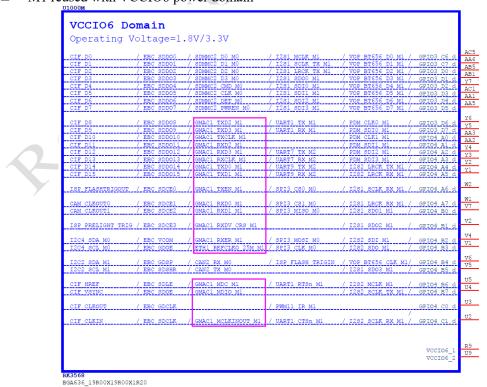

| Figure 2-138 The decoupling capacitors of RK3568 VCCIO6 power supply            | 116             |

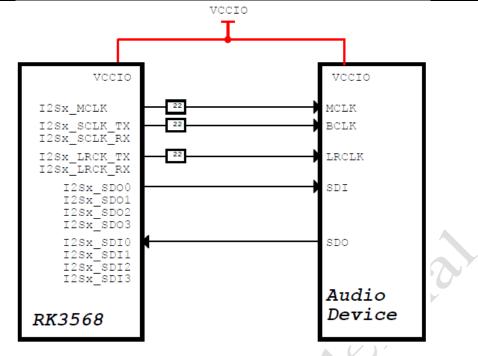

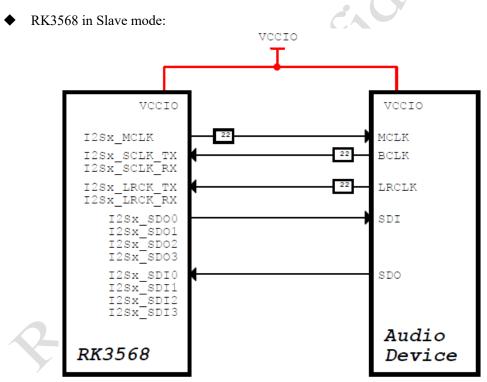

| Figure 2-139 Connection diagram of RK3568 I2S in Master mode                    | 120             |

| Figure 2-140 Connection diagram of RK3568 I2S in Slave mode                     |                 |

| Figure 2-141 RK3568 I2S1 M0 functional pins                                     | 121             |

| Figure 2-142 RK3568 I2S1 M1 functional pins                                     | 121             |

| Figure 2-143 RK3568 I2S1 M2 functional pins                                     |                 |

| Figure 2-144 RK3568 I2S2 M0 functional pins                                     | 124             |

| Figure 2-145 RK3568 I2S2 M1 functional pins                                     | 124             |

| Figure 2-146 RK3568 I2S3 M0 functional pins                                     |                 |

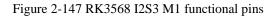

| Figure 2-147 RK3568 I2S3 M1 functional pins                                     |                 |

| Figure 2-148 RK3568 PDM M0 functional pins                                      | 127             |

| Figure 2-149 RK3568 PDM M1 functional pins                                      |                 |

| Figure 2-150 RK3568 PDM M2 functional pins                                      |                 |

| Figure 2-151 Process mode of related pins when RK809-5 Codec module is not used | 130             |

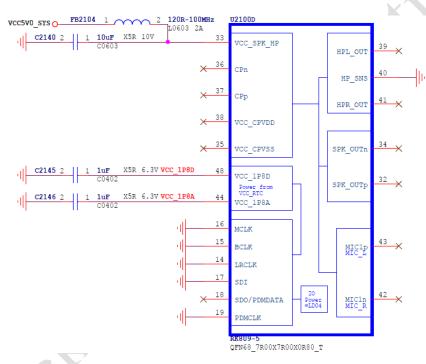

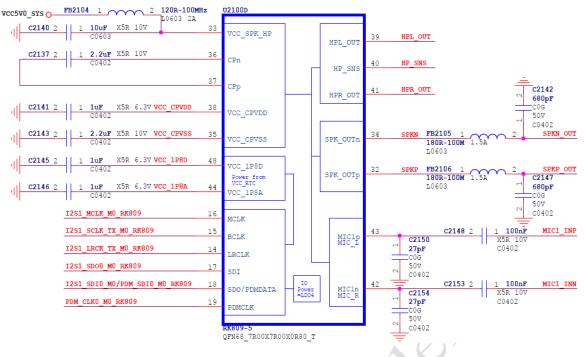

| Figure 2-152 RK809-5 Codec module                                               | 131             |

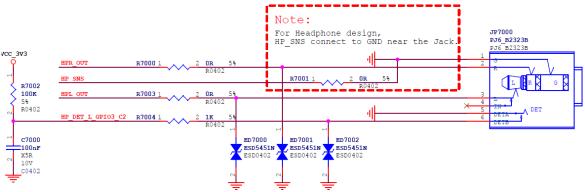

| Figure 2-153 RK809 Codec output earphone circuit                                | 132             |

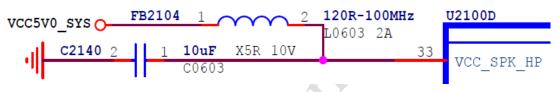

| Figure 2-154 RK809-5 SPK/HP power supply pins                                   |                 |

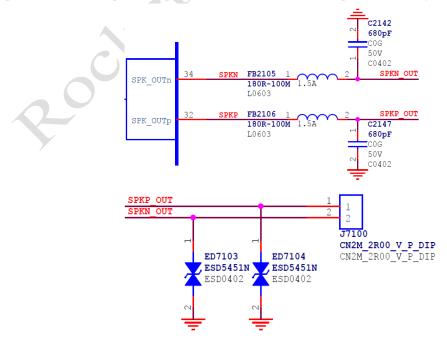

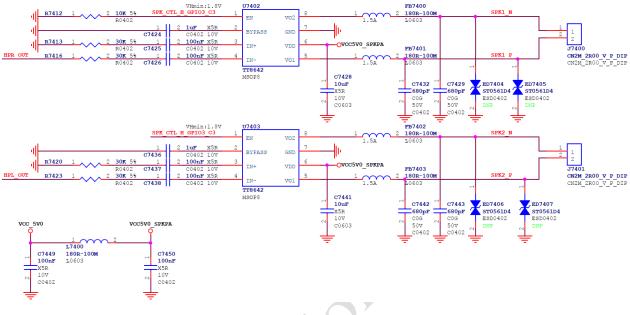

| Figure 2-155 RK809-5 SPK output circuit                                         | 132             |

| Copyright © 2022 Rockchip Electronics Co., Ltd.                                 | XI              |

| RK3568 Hardware Design Guide                                               | <i>Rev V1.2</i> |

|----------------------------------------------------------------------------|-----------------|

| Figure 2-156 External SPK circuit                                          |                 |

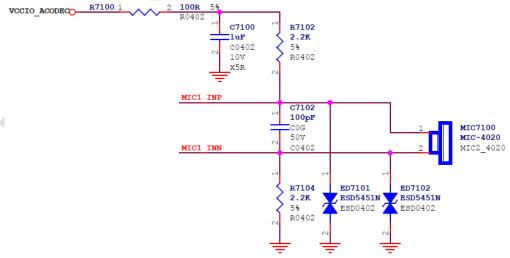

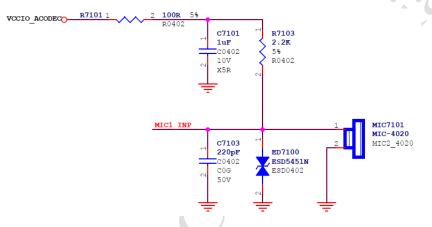

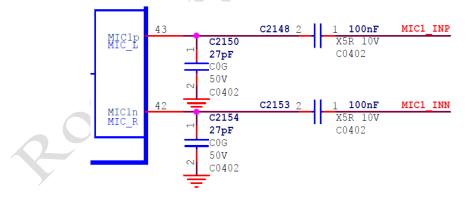

| Figure 2-157 Electret MIC differential input circuit                       |                 |

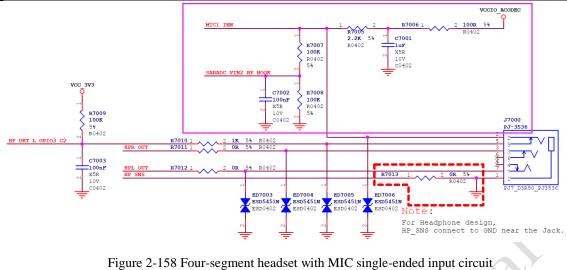

| Figure 2-158 Four-segment headset with MIC single-ended input circuit      | 134             |

| Figure 2-159 Electret MIC single-ended input circuit                       | 134             |

| Figure 2-160 RK809-5 MIC input circuit pins                                | 134             |

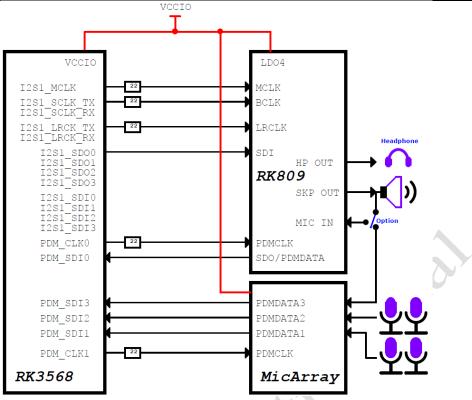

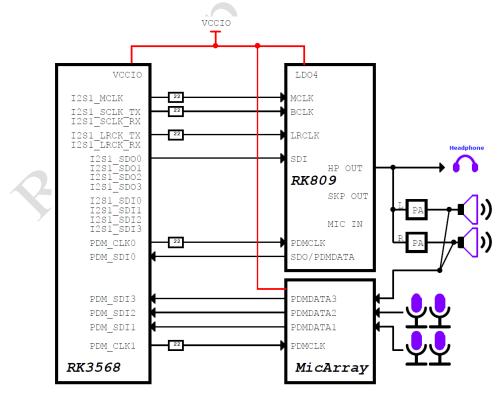

| Figure 2-161 Array MIC solution I2S/PDM connection diagram 1               |                 |

| Figure 2-162 Array MIC solution I2S/PDM connection diagram 2               | 136             |

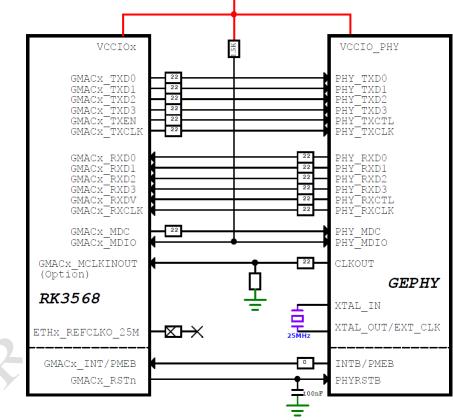

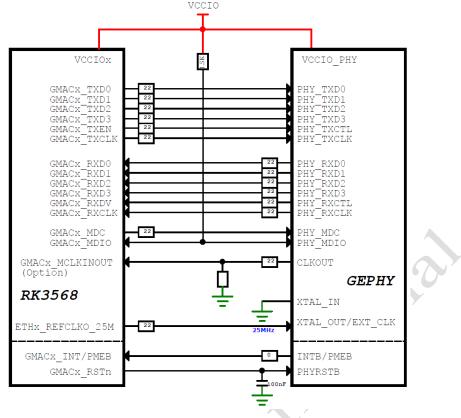

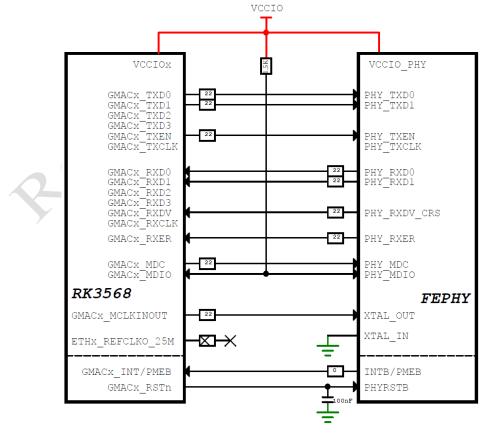

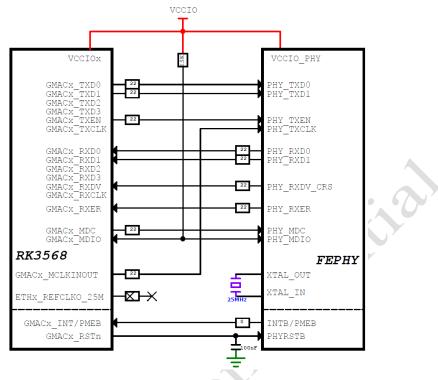

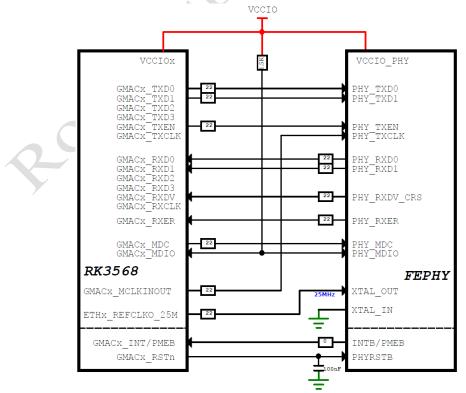

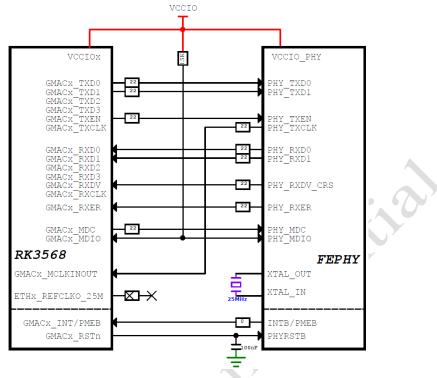

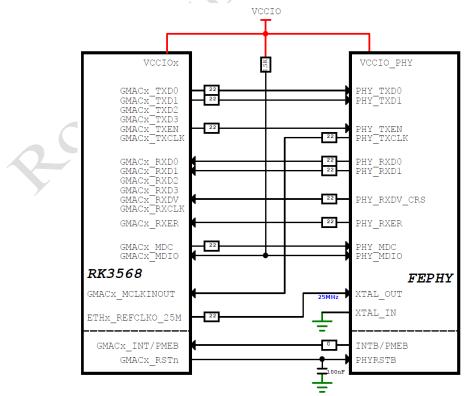

| Figure 2-163 Path block diagram of RK3568 GMAC0, GMAC1 reused with IO      | 137             |

| Figure 2-164 RK3568 GMAC0 functional pins                                  | 137             |

| Figure 2-165 RK3568 GMAC1 M0 functional pins                               | 138             |

| Figure 2-166 RK3568 GMAC1 M1 functional pins                               |                 |

| Figure 2-167 RGMII connection example 1                                    |                 |

| Figure 2-168 RGMII connection example 2                                    | 141             |

| Figure 2-169 RMII connection example 1                                     | 141             |

| Figure 2-170 RMII connection example 2                                     | 142             |

| Figure 2-171 RMII connection example 3                                     | 142             |

| Figure 2-172 RMII connection example 4                                     |                 |

| Figure 2-173 RMII connection example 5                                     | 143             |

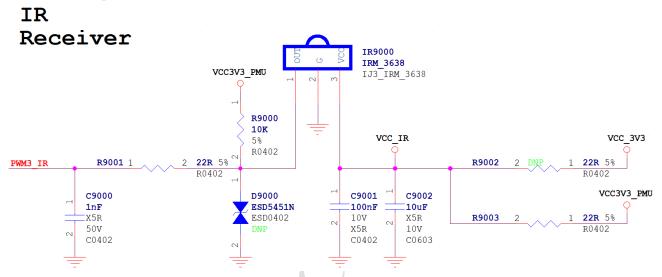

| Figure 2-174 IR receiver circuit                                           |                 |

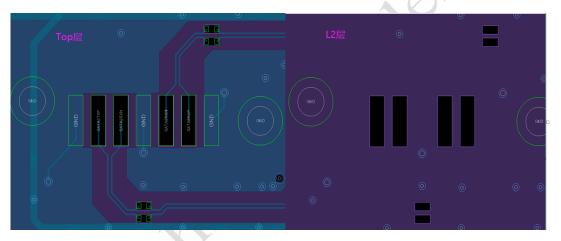

| Figure 3-1 Six layers PCB design                                           |                 |

| Figure 3-2 Four layers PCB design                                          | 152             |

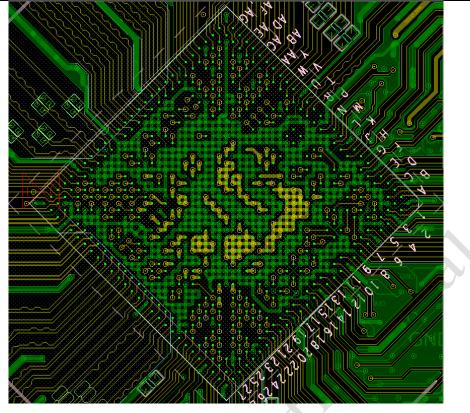

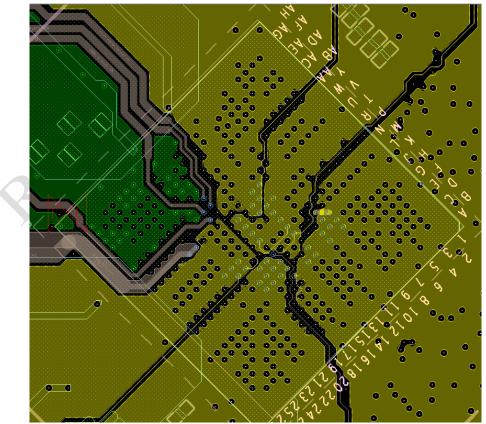

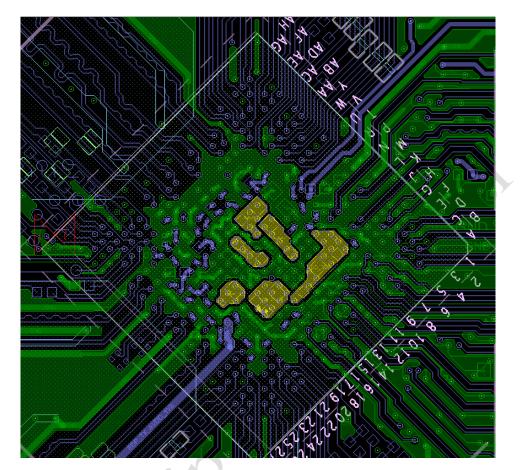

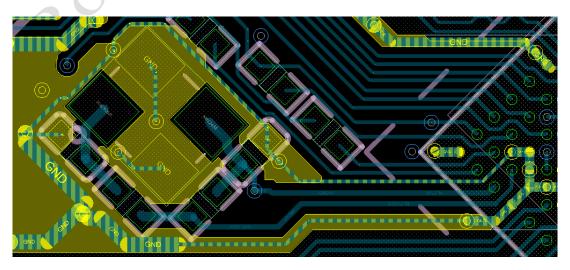

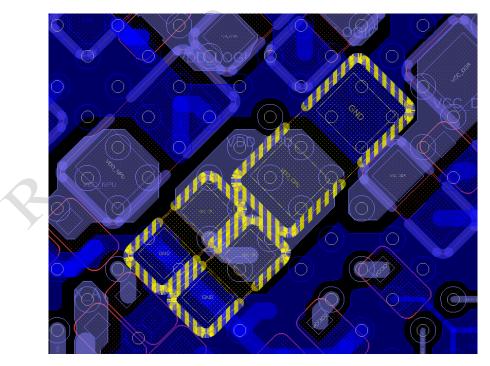

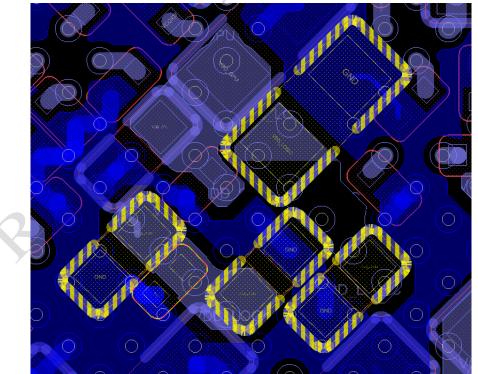

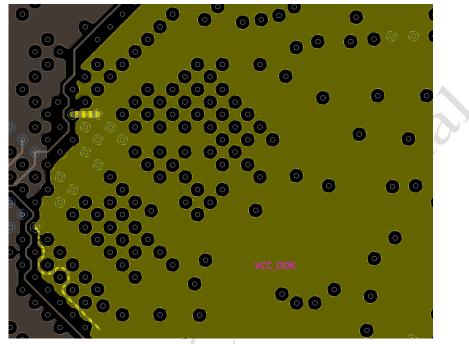

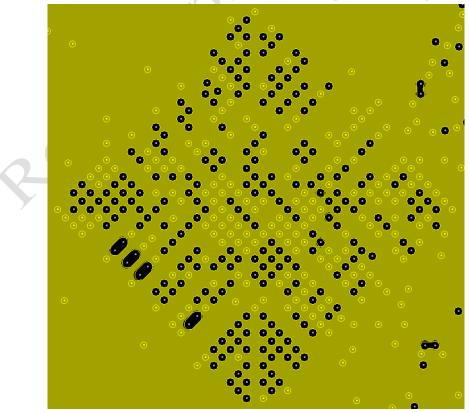

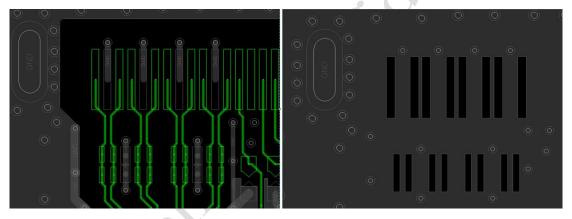

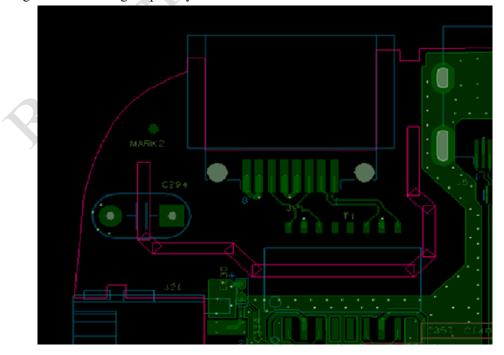

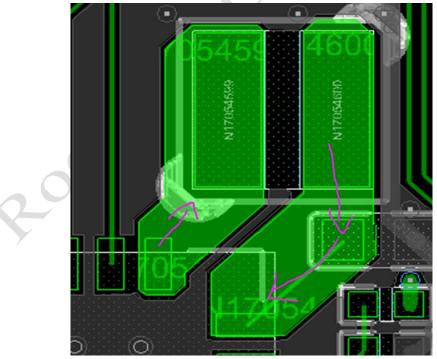

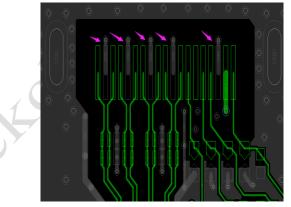

| Figure 3-3 RK3568 Fan-out diagram 1                                        |                 |

| Figure 3-4 RK3568 Fan-out diagram 2                                        |                 |

| Figure 3-5 RK3568 Fan-out diagram 3                                        | 154             |

| Figure 3-6 RK3568 Fan-out diagram 4                                        | 155             |

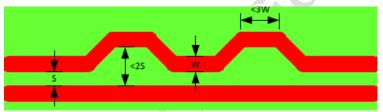

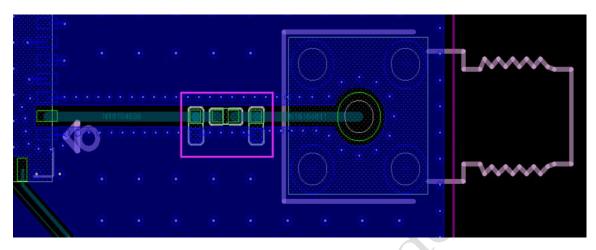

| Figure 3-7 A diagram of space between signals                              | 155             |

| Figure 3-8 A diagram of equal length within and between differential pairs | 156             |

| Figure 3-9 A diagram of differential pair length compensation requirements |                 |

| Figure 3-10 Stitching vias requirement diagram                             | 156             |

| Figure 3-11 Edge requirement of signal reference plane diagram             | 157             |

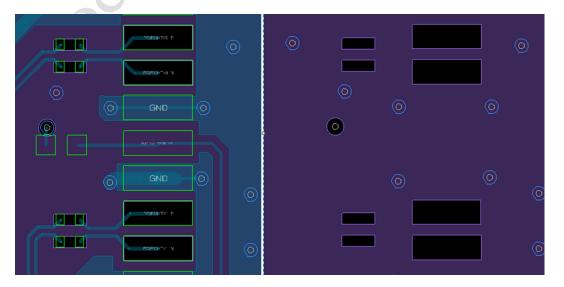

| Figure 3-12 RK3568 Crystal layout and routing                              | 157             |

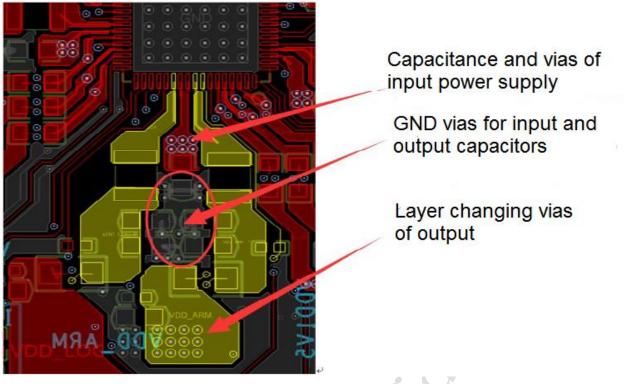

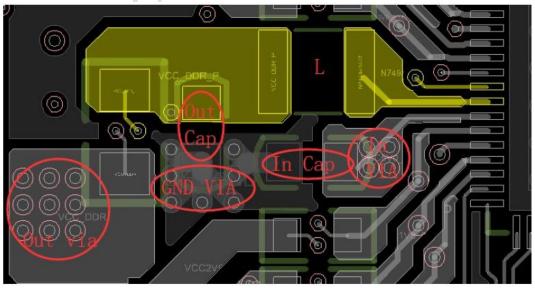

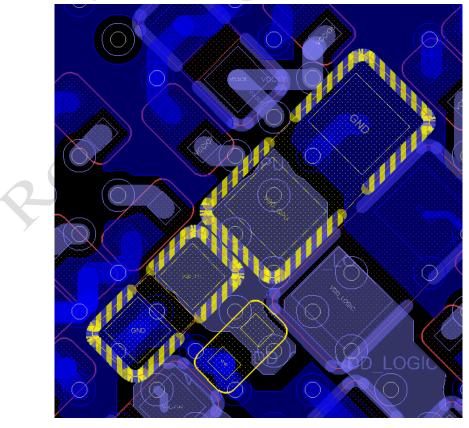

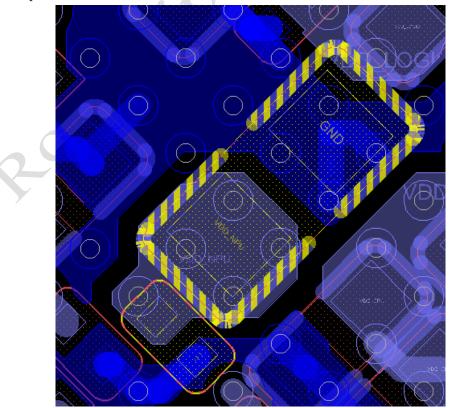

| Figure 3-13 RK809-5 BUCK1/BUCK2 Layout and routing                         | 159             |

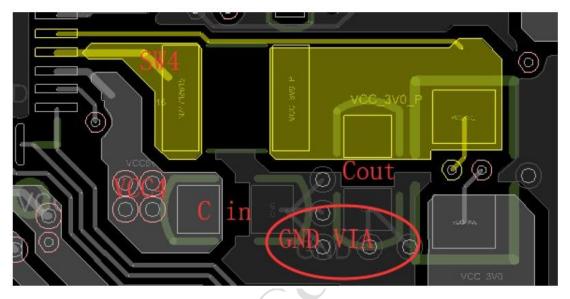

| Figure 3-14 RK809-5 BUCK3 Layout and routing                               | 159             |

| Figure 3-15 RK809-5 BUCK4 Layout and routing                               | 160             |

| Figure 3-16 RK809-5 BUCK5 Layout and routing                               | 161             |

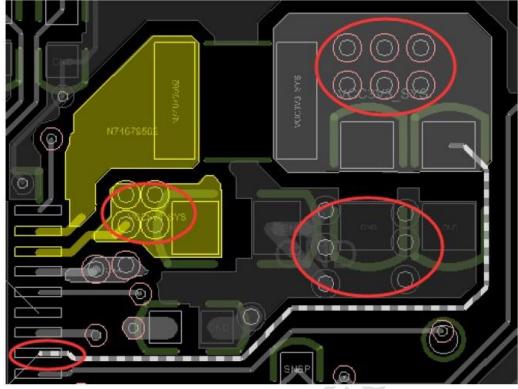

| Figure 3-17 RK809-5 EPAD vias layout                                       | 162             |

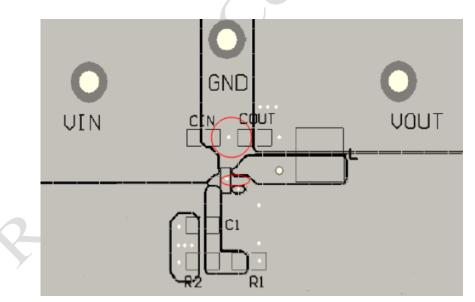

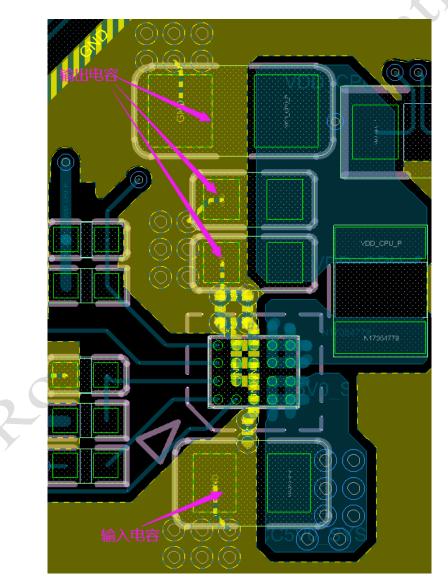

| Figure 3-18 Discrete power supply DC/DC layout and routing                 | 162             |

| Figure 3-19 VDD_CPU Power supply DC/DC layout and tracing                  |                 |

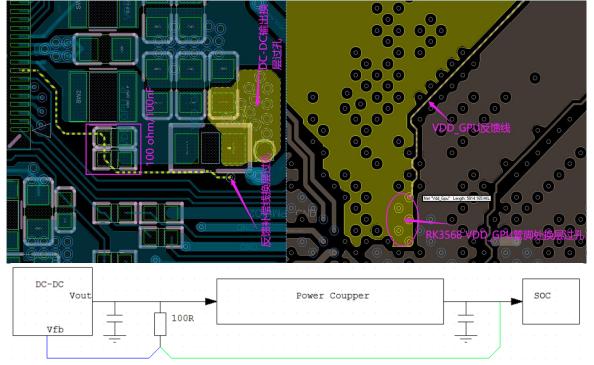

| Figure 3-20 A diagram of DC/DC remote feedback design                      | 164             |

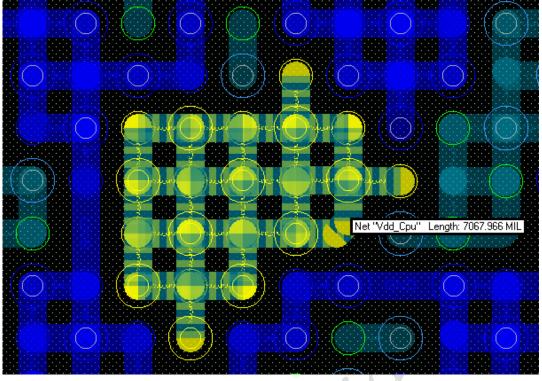

| Figure 3-21 RK3568 VDD_CPU Power pin routing and vias                      | 165             |

| Copyright © 2022 Rockchip Electronics Co., Ltd.                            | XII             |

| RK3568 Hardware Design Guide                                                                      | <i>Rev V1.2</i> |

|---------------------------------------------------------------------------------------------------|-----------------|

| Figure 3-22 Placement of decoupling capacitors on the back of RK3568 VDD_CPU power pins           |                 |

| Figure 3-23 Copper-covering on RK3568 VDD_CPU power layer                                         |                 |

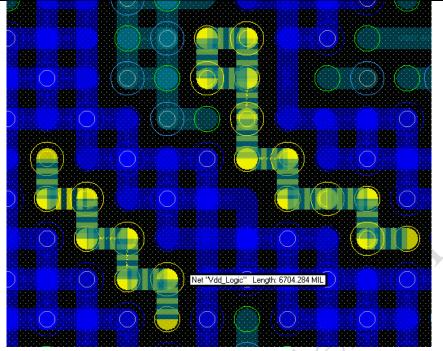

| Figure 3-24 RK3568 VDD_LOGIC power supply pin routing and vias                                    | 167             |

| Figure 3-25 Placement of decoupling capacitors on the back of RK3568 VDD_LOGIC power pins         | 167             |

| Figure 3-26 Copper-covering on RK3568 VDD_LOGIC power layer                                       |                 |

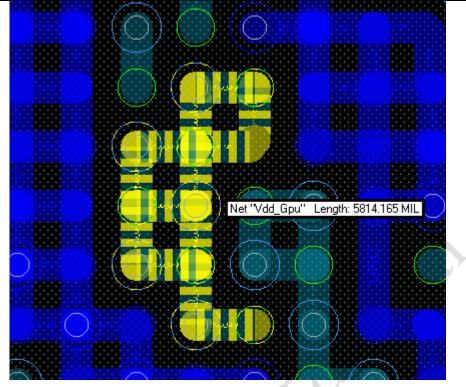

| Figure 3-27 RK3568 VDD_GPU Power pin traces and vias                                              |                 |

| Figure 3-28 Placement of decoupling capacitors on the back of RK3568 VDD_GPU power pins           |                 |

| Figure 3-29 Copper covering on RK3568 VDD_GPU power layer                                         | 170             |

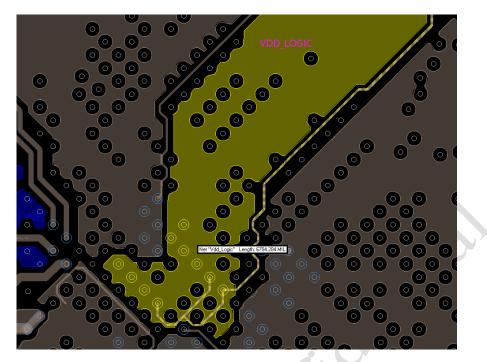

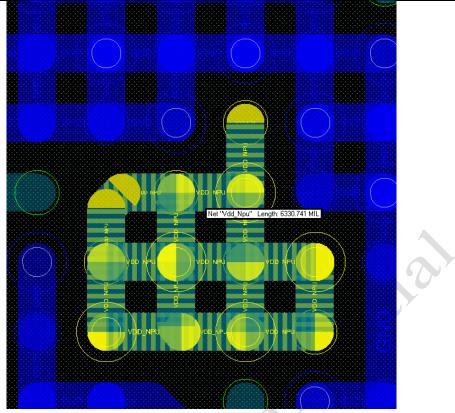

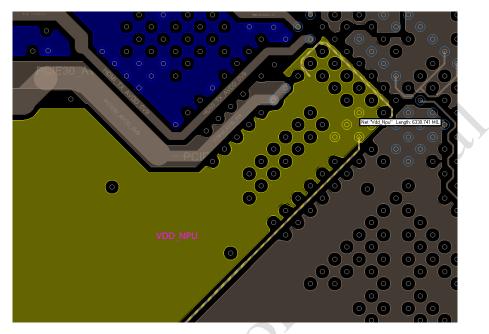

| Figure 3-30 RK3568 VDD_NPU Power pin routing and vias                                             | 171             |

| Figure 3-31 Placement of decoupling capacitors on the back of VDD_NPU power                       | 171             |

| Figure 3-32 Copper covering on RK3568 VDD_NPU power layer                                         | 172             |

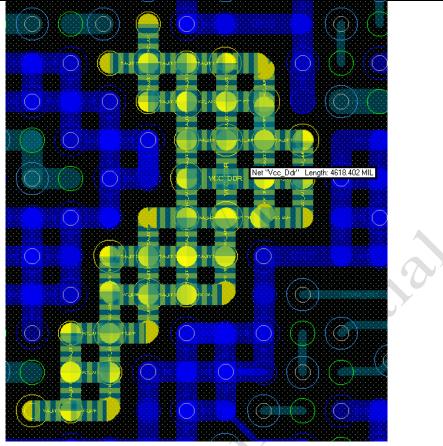

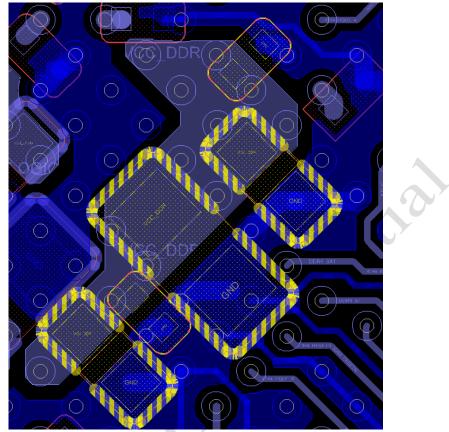

| Figure 3-33 RK3568 VCC_DDR power pin routing and vias                                             | 173             |

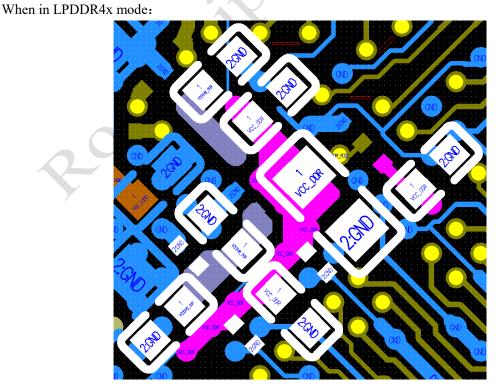

| Figure 3-34 RK3568 VCC_DDR/VCC0V6_DDR Power pin routing and vias in LPDDR4x mode                  |                 |

| Figure 3-35 Placement of decoupling capacitor on the back of the power supply pin of RK3568 VCC_D | DR174           |

| Figure 3-36 Placement of decoupling capacitors on the back of the power supply                    | pins of         |

| VCC_DDR/VCC0V6_DDR of RK3568 in LPDDR4x mode                                                      | 174             |

| Figure 3-37 Copper covering on RK3568 VCC_DDR power layer                                         | 175             |

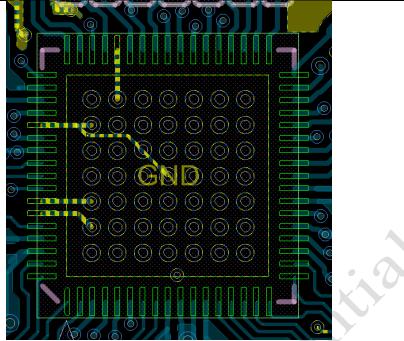

| Figure 3-38 RK3568 VSS pin routing and vias                                                       | 176             |

| Figure 3-39 Ground copper-covering of RK3568                                                      |                 |

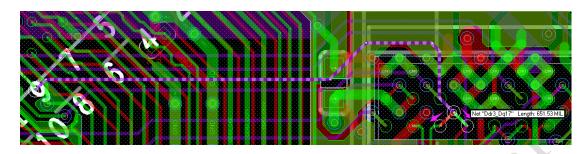

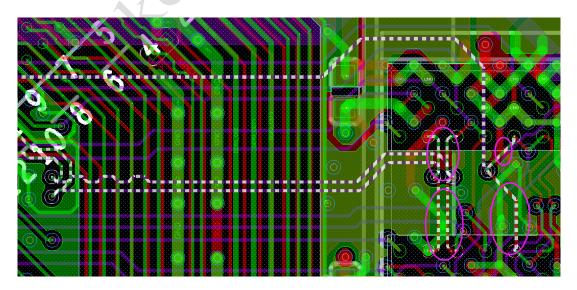

| Figure 3-40 DDR3/DDR3L DQS/DQ/DM signal routing topology                                          | 178             |

| Figure 3-41 DDR3/DDR3L CLK signal routing topology                                                | 179             |

| Figure 3-42 DDR3/DDR3L CLK signal RC circuit                                                      | 179             |

| Figure 3-43 DDR3/DDR3L CSn/CKE/ODT signal routing topology                                        |                 |

| Figure 3-44 Other CA/CMD signal of DDR3/DDR3L routing topology except CSn/CKE/ODT                 |                 |

| Figure 3-45 DDR3/DDR3L+ECC DQS/DQ/DM signal routing topology                                      |                 |

| Figure 3-46 DDR3/DDR3L+ECC CLK signal routing topology                                            |                 |

| Figure 3-47 DDR3/DDR3L+ECC CSn/CKE/ODT signal routing topology                                    |                 |

| Figure 3-48 DDR3/DDR3L+ECC other CA/CMD signal routing topology except CSn/CKE/ODT                |                 |

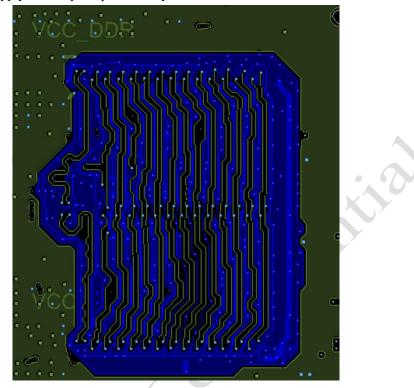

| Figure 3-49 DDR4 DQS/DQ/DM signal routing topology                                                |                 |

| Figure 3-50 DDR4 CLK signal routing topology                                                      |                 |

| Figure 3-51 RC circuit for DDR4 CLK signal                                                        |                 |

| Figure 3-52 CLK/CA/CMD signal routing diagram on the L3 plane of DDR4 4-layer board               |                 |

| Figure 3-53 DDR4 CSn/CKE/ODT signal routing topology                                              |                 |

| Figure 3-54 Other CA /CMD signal routing topologies except CSN/CKE/ODT when using DDR4            |                 |

| Figure 3-55 DDR4+ECC DQS/DQ/DM signal routing topology                                            |                 |

| Figure 3-56 DDR4+ECC CLK signal routing topology                                                  |                 |

| Figure 3-57 DDR4+ECC CSn/CKE/ODT signal routing topology                                          | 191             |

| Figure 3-58 DDR4+ECC other CA/CMD signal routing topology except CSn/CKE/ODT                      |                 |

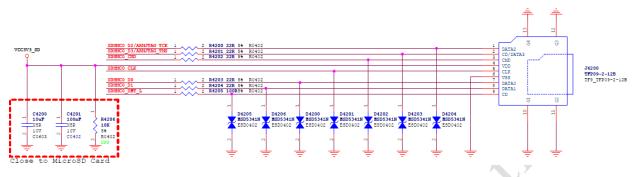

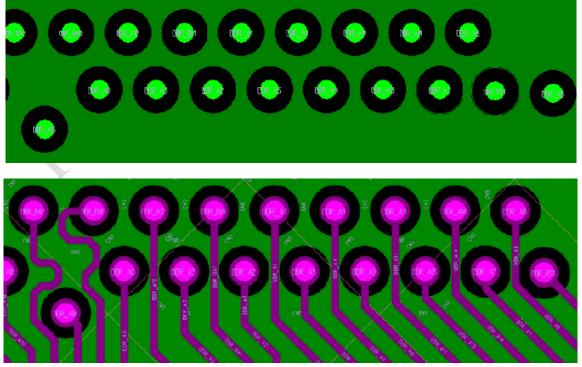

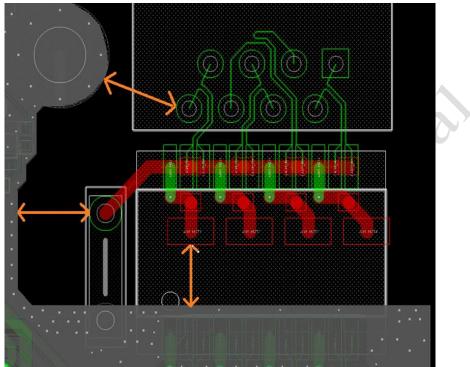

| Figure 3-59 Branch resistances of eMMC and Nand Flash compatible design                           | 197             |

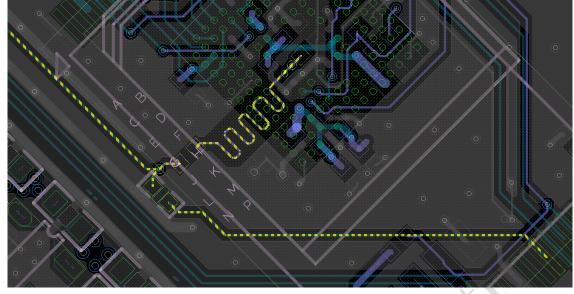

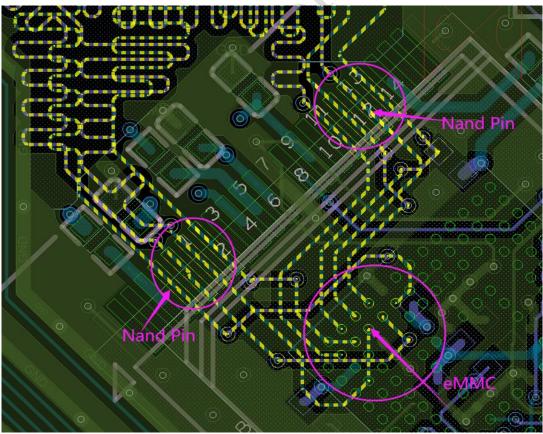

| Figure 3-60 Branch resistor layout and routing of eMMC and NAND flash compatible design           |                 |

| Copyright © 2022 Rockchip Electronics Co., Ltd.                                                   | XIII            |

| RK3568 Hardware Design GuideR                                                                         | ev V1.2   |

|-------------------------------------------------------------------------------------------------------|-----------|

| Figure 3-61 Figure 3–61 DATA routing of eMMC and Nand Flash compatible design                         | 198       |

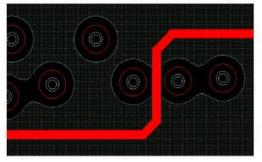

| Figure 3-62 Schematic diagram of empty space below the pad of USB3 connector and the pad of AC        | coupling  |

| capacitor                                                                                             | 202       |

| Figure 3-63 PCB fiberweave effect to improve routing way                                              | 202       |

| Figure 3-64 Schematic diagram of empty space below the pad of SATA connector and the pad of AC        | coupling  |

| capacitor                                                                                             | 203       |

| Figure 3-65 Schematic diagram of empty space below the pad of PCIe Slot and the pad of AC coupling of | capacitor |

|                                                                                                       | 205       |

| Figure 3-66 Schematic diagram of empty space below the pad of HDMI connector and the pad of TVS dic   | ode.211   |

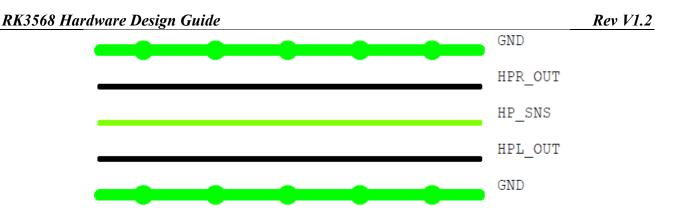

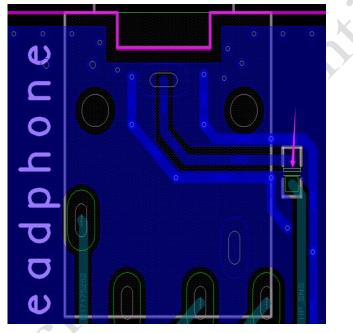

| Figure 3-67 RK809-5 HP_SNS resistor layout and routing                                                | 213       |

| Figure 3-68 RK809-5 HPL/HPR/HP_SNS routing                                                            | 213       |

| Figure 3-69 Schematic diagram of prohibited routing area for RJ45 interface and network transformer   | 217       |

| Figure 3-70 Schematic diagram of RJ45 interface and network transformer slotting                      | 217       |

| Figure 3-71 Schematic diagram of inductance and capacitance of the WIFI module routing                | 218       |

| Figure 3-72 Schematic diagram of WIFI module antenna routing                                          | 219       |

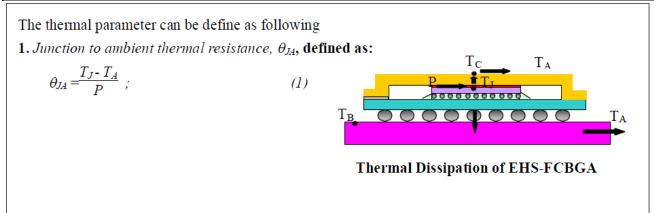

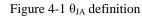

| Figure 4-1 $\theta_{JA}$ definition                                                                   | 222       |

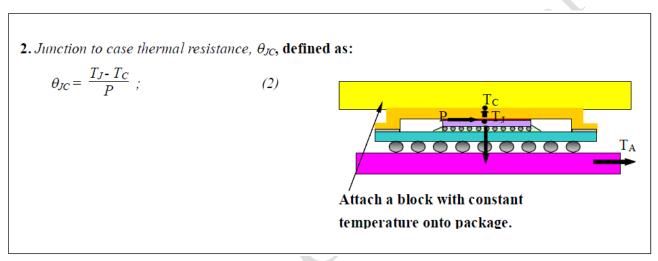

| Figure 4-2 $\theta_{JC}$ definition                                                                   | 222       |

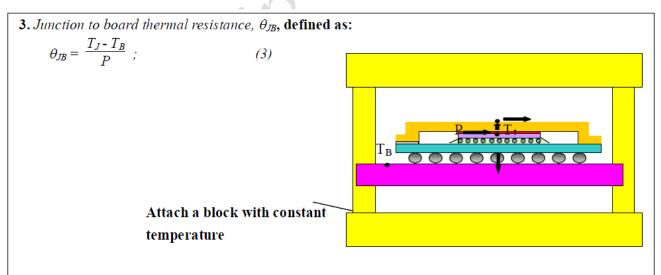

| Figure 4-3 $\theta_{JB}$ definition                                                                   |           |

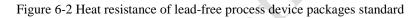

| Figure 6-1 Reflow soldering profile classification                                                    | 230       |

| Figure 6-2 Heat resistance of lead-free process device packages standard                              | 230       |

| Figure 6-3 Lead-free reflow profile                                                                   | 230       |

| Figure 6-4 Lead-free reflow soldering process recommended profile parameters                          | 231       |

| Figure 7-1 Chipset dry vacuum package                                                                 | 233       |

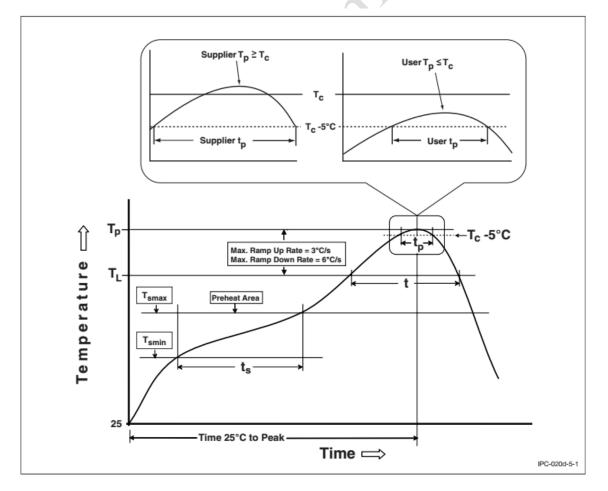

| Figure 7-2 Six-point humidity card                                                                    | 233       |

| Figure 7-1 Chipset dry vacuum package<br>Figure 7-2 Six-point humidity card                           |           |

## **Tables**

| Table 2–1 RK3568 24MHz clock requirements                                             | 4   |

|---------------------------------------------------------------------------------------|-----|

| Table 2–2 RK3568 32.768KHz clock requirements                                         | 5   |

| Table 2–3 RK3568 System initialization configuration signal description               | 10  |

| Table 2–4 RK3568 JTAG debug interface signal                                          |     |

| Table 2–5 RK3568 DDR PHY I/O map                                                      | 12  |

| Table 2–6 RK3568 eMMC interface design                                                | 26  |

| Table 2–7 RK3568 FSPI interface design                                                | 29  |

| Table 2–8 RK3568 Nand Flash interface design                                          | 31  |

| Table 2–9 RK3568 GPIO power pins description                                          | 33  |

| Table 2–10 RK3568 power supply requirements                                           |     |

| Table 2–11 RK3568 power supply requirement of each module for the first powered on    | 37  |

| Table 2–12 RK3568 standby power supply requirements                                   |     |

| Table 2–13 RK3568 internal PLL Introduction      Table 2–14 RK3568 peak current table |     |

| Table 2–14 RK3568 peak current table                                                  | 63  |

| Table 2–15 SDMMC0 interface design                                                    | 65  |

| Table 2–16 SDMMC1 interface design                                                    | 66  |

| Table 2–17 SDMMC2 interface design                                                    | 68  |

| Table 2–18 RK3568 USB2.0/USB3.0 interface design                                      | 78  |

| Table 2–19 RK3568 SATA interface design                                               | 81  |

| Table 2–20 RK3568 QSGMII/SGMII interface design                                       | 87  |

| Table 2–21 RK3568 PCIe2.0 interface design.                                           | 89  |

| Table 2–22 RK3568 PCIe3.0 interface design                                            | 92  |

| Table 2–23 RK3568 MIPI CSI RX interface design.                                       | 94  |

| Table 2–24 RK3568 Data relationship in BT1120 16bit mode                              | 96  |

| Table 2–25 RK3568 CIF interface design                                                | 97  |

| Table 2–26 RK3568 HDMI2.0 TX interface design                                         | 102 |

| Table 2–27 RK3568 MIPI DSI TX0 and LVDS TX Combo PHY interfaces design                | 104 |

| Table 2–28 RK3568 MIPI DSI TX1 PHY interface design                                   | 105 |

| Table 2–29 RK3568 eDP TX PHY interface design                                         | 107 |

| Table 2–30 RK3568 parallel RGB interface formats                                      | 108 |

| Table 2–31 RK3568 parallel RGB interface design                                       | 110 |

| Table 2–32 RK3568 BT1120 output formats                                               |     |

| Table 2–33 RK3568 BT1120 output interface design.                                     | 112 |

| Table 2–34 RK3568 BT656 output interface design                                       | 115 |

| Table 2–35 RK3568 EBC output interface design                                         | 117 |

| Table 2–36 RK3568 I2S1 interface design                                               |     |

| Table 2–37 RK3568 I2S2 interface design                                               | 125 |

| Table 2–38 RK3568 I2S3 interface design                                               | 127 |

| RK3568 Hardware Design Guide                                                                | <i>Rev V1.2</i> |

|---------------------------------------------------------------------------------------------|-----------------|

| Table 2–39 RK3568 PDM interface design                                                      | 129             |

| Table 2-40 RK3568 SPDIF interface design                                                    | 130             |

| Table 2-41 RK3568 matching relationship between audio applications and the circuit diagram  | 135             |

| Table 2–42 RK3568 RGMII/RMII interface design                                               | 139             |

| Table 2–43 RK3568 UART interface distribution                                               | 145             |

| Table 2-44 RK3568 UART interface design                                                     | 145             |

| Table 2–45 RK3568 SPI interface distribution                                                | 146             |

| Table 2–46 RK3568 SPI interface design                                                      | 146             |

| Table 2–47 RK3568 CAN interface distribution                                                | 147             |

| Table 2–48 RK3568 CAN interface design                                                      | 147             |

| Table 2–49 RK3568 I2C interface distribution                                                | 148             |

| Table 2–50 RK3568 I2C interface design                                                      | 148             |

| Table 2–51 RK3568 PWM interface distribution                                                | 149             |

| Table 3-1 DDR3/DDR3L DQS/DQ/DM signal impedance and routing requirements                    | 179             |

| Table 3-2 DDR3/DDR3L CLK signal impedance and routing requirements                          |                 |

| Table 3-3 DDR3/DDR3L CSn/CKE/ODT signal impedance and routing requirements                  |                 |

| Table 3-4 Other CA/CMD signal of DDR3/DDR3L routing topology except CSn/CKE/ODT             |                 |

| Table 3-5 DDR3/DDR3L+ECC DQS/DQ/DM signal impedance and routing requirements                |                 |

| Table 3-6 DDR3/DDR3L+ECC CLK signal impedance and routing requirements                      |                 |

| Table 3-7 DDR3/DDR3L+ECC CSn/CKE/ODT signal impedance and routing requirements              |                 |

| Table 3-8 DDR3/DDR3L+ECC other CA/CMD signal impedance and routing requirement              | ts except       |

| CSn/CKE/ODT                                                                                 | 184             |

| Table 3-9 LPDDR3 signal impedance and routing requirements                                  | 184             |

| Table 3-10 DDR4 DQS/DQ/DM signal impedance and routing requirements                         |                 |

| Table 3-11 DDR4 CLK signal impedance and routing requirements                               | 187             |

| Table 3-12 DDR4 CSn/CKE/ODT signal impedance and routing requirements                       |                 |

| Table 3–13 Other CA /CMD signal routing topologies except CSN/CKE/ODT when using DDR4       |                 |

| Table 3-14 DDR4+ECC DQS/DQ/DM signal impedance and routing requirements                     | 190             |

| Table 3–15 DDR4+ECC CLK signal impedance and routing requirements                           | 191             |

| Table 3-16 DDR4+ECC CSn/CKE/ODT signal impedance and routing requirements                   | 191             |

| Table 3-17 DDR4+ECC other CA/CMD signal impedance and routing requirements except CSn/CKE/C | DDT192          |

| Table 3–18 LPDDR4 signal impedance and routing requirements                                 | 192             |

| Table 3–19 LPDDR4 signal impedance and routing requirements                                 | 193             |

| Table 3-20 eMMC signal impedance and routing requirements                                   | 194             |

| Table 3-21 FSPI signal impedance and routing requirements                                   | 195             |

| Table 3-22 Nand Flash signal impedance and routing requirements                             | 196             |

| Table 3–23 SDMMC0/1/2 signal impedance and routing requirements                             | 199             |

| Table 3-24 USB2.0 signal impedance and routing requirements                                 |                 |

| Table 3-25 USB3.0 signal impedance and routing requirements                                 | 201             |

| Table 3–26 SATA3.0 signal impedance and routing requirements                                |                 |

| Copyright © 2022 Rockchip Electronics Co., Ltd.                                             | XVI             |

| RK3568 Hardware Design Guide                                          | <i>Rev V1.2</i> |

|-----------------------------------------------------------------------|-----------------|

| Table 3-27 QSGMII/SGMII signal impedance and routing requirements     |                 |

| Table 3–28 PCIe2.0 signal impedance and routing requirements          |                 |

| Table 3–29 PCIe3.0 signal impedance and routing requirements          |                 |

| Table 3–30 MIPI CSI RX signal impedance and routing requirements      | 207             |

| Table 3–31 CIF signal impedance and routing requirements              |                 |

| Table 3–32 MIPI DSI TX signal impedance and routing requirements      |                 |

| Table 3–33 LVDS TX signal impedance and routing requirements          |                 |

| Table 3–34 eDP TX signal impedance and routing requirements           | 210             |

| Table 3–35 HDMI TX signal impedance and routing requirements          | 210             |

| Table 3–36 RGB TX signal impedance and routing requirements           |                 |

| Table 3–37 BT1120 TX signal impedance and routing requirements        |                 |

| Table 3–38 RGMII signal impedance and routing requirements            | 214             |

| Table 3–39 RMII signal impedance and routing requirements             |                 |

| Table 4–1 RK3568 thermal resistance simulation report results         |                 |

| Table 4–2 RK3568 PCB structure used for thermal resistance simulation |                 |

| Table 7–1 Moisture Sensitivity Levels (MSL)                           | 234             |

| Table 7–2 RV11XX chipset Re-bake reference table                      | 234             |

| COR                                                                   |                 |

| e ching                                                               |                 |

#### **1** System Introduction

#### 1.1 Overview

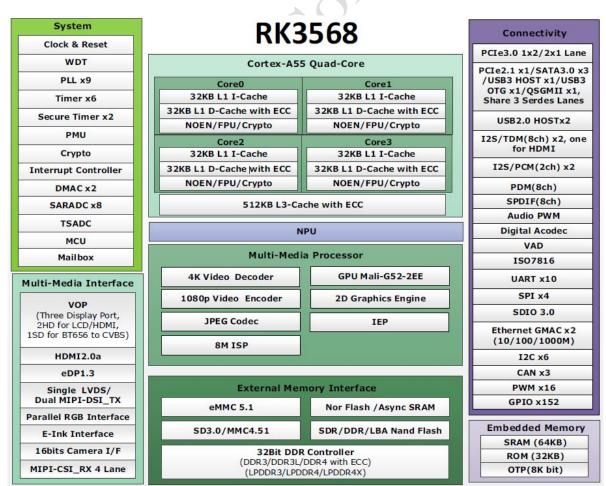

RK3568 is a low-power and high-performance processor designed for personal mobile Internet devices and AIoT devices.

RK3568 provides many powerful embedded hardware engines to optimize the performance of advanced applications. RK3568 supports almost all formats of H.264 4k@60fps decoding, and supports H.265 4k@60fps decoding, H.264/H.265 1080p@60fps encoding, and high-quality JPEG encoding/decoding.

RK3568 embedded 3D GPU is fully compatible with OpenGL ES 1.1/2.0/3.2, OpenCL 2.0 and Vulkan 1.1; the special 2D hardware engine maximizes the display performance and provides a smooth operating experience also.

The built-in NPU supports INT8/INT16 mixed operation. Due to strong compatibility, network models based on a series of frameworks such as TensorFlow/MXNet/PyTorch/Caffe can be easily converted.

There are high-performance external memory interfaces in RK3568 to ensure high-capacity and high-stability system operating memory bandwidth, and it supports multiple memory models such as DDR3, DDR3L, LPDDR3, DDR4, LPDDR4, LPDDR4X, etc.

#### **1.2 Block Diagram**

Figure 1-1 RK3568 block diagram

#### **1.3 Application Block Diagram**

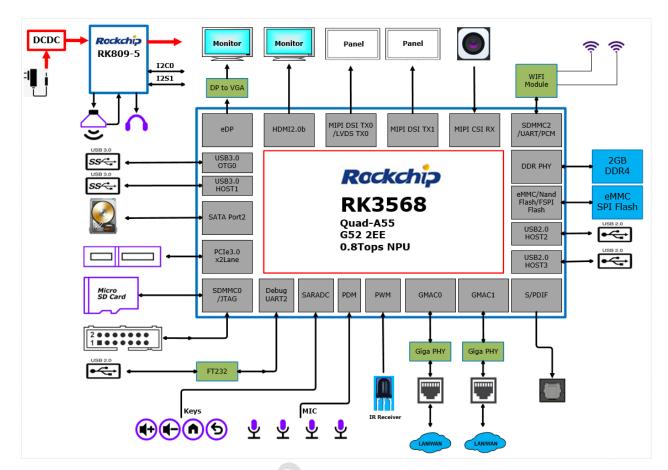

#### 1.3.1 RK3568 EVB Application Block Diagram

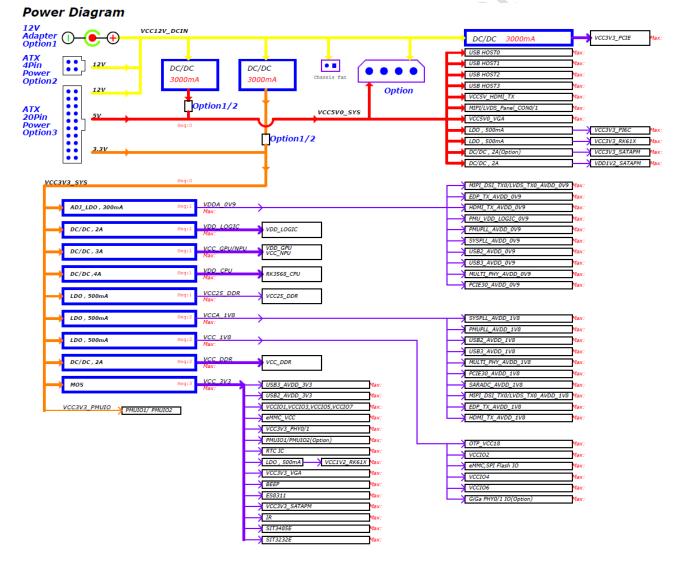

Figure 1-2 RK3568 EVB application block diagram

Rockey

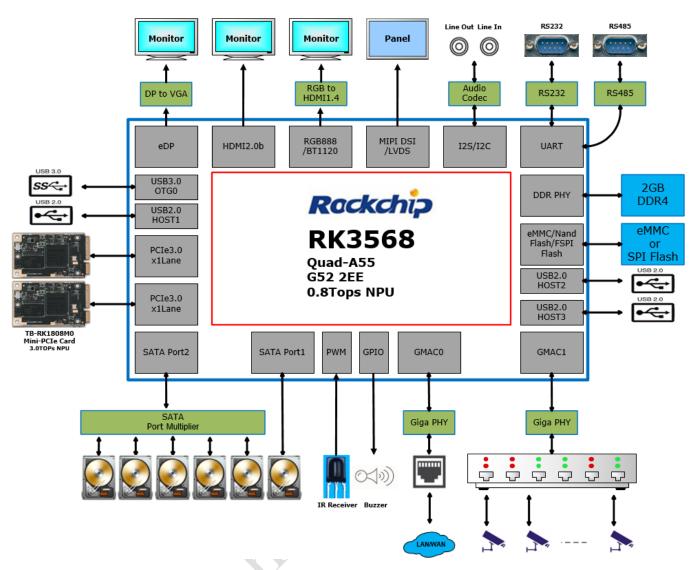

1.3.2 RK3568 Smart NVR Application Block Diagram

Figure 1-3 RK3568 Smart NVR application block diagram

The figures above are example application block diagrams of RK3568, please refer to the reference design schematic released by RK for more details.

#### 2 Schematic Design Recommendation

#### 2.1 Minimum System Design

#### 2.1.1 Clock Circuit

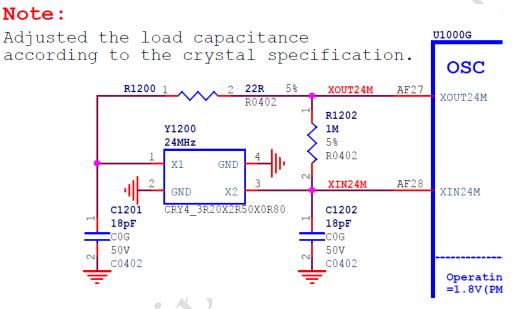

- The oscillator circuit inside RK3568 and the external 24MHz crystal form the system clock, as shown in Figure 2-1.

- The 220hm resistor connected to the XOUT24M network in series must be added to limit current and prevent overdrive.

- The 1M ohm resistor between XOUT24M and XIN24M network cannot be modified at will.

The load capacitances of crystal should be selected according to the CL capacitance value of the crystal actually used, and the frequency tolerance at room temperature should be controlled within 20ppm.

18pF is the capacitance value of the crystal selected by RK, not a general value, and COG or NPO material are recommended. It is recommended to use 4Pin SMT crystal, with 2 GND pins fully connected with the ground of the PCB to enhance ESD anti-interference ability

• The system clock can also be directly generated by an external active crystal circuit with a clock amplitude of 1.8V. When working, the clock is input through the XIN24M pin, and the XOUT24M pin can be floated. The clock parameters are shown in the following Table 2-1:

|                       | 14010 2 | 1100550021011 | 2 elock requireme | 21105        |

|-----------------------|---------|---------------|-------------------|--------------|

| Parameters            |         | Spec          | Description       |              |

| rarameters            | Min.    | Max.          | Unit              | Description  |

| Frequency             | 2       | 4.000000      | MHz               |              |

| Frequency tolerance   |         | +/-20         | ppm               |              |

| Clock amplitude       |         | 1.8           | V                 | Peak-to-peak |

| Operating temperature | -20     | 80            | °C                |              |

| ESR                   | /       | 40            | Ohm               |              |

Table 2-1 RK3568 24MHz clock requirements

- When RK3568 is in standby, you can choose to switch the working clock source to the clock provided by the PMU\_PVTM module or an external 32.768KHz clock. Turn off the OSC oscillator circuit to get better standby power consumption. At this time, only the IO interrupt in the PMUIO1 and PMUIO2 power domain are supported to wake up. If the required wake-up source is related to the 24MHz clock, the 24MHz clock cannot be turned off.

- The clock oscillation loop integrated in PVTM (Process-Voltage-Temperature Monitor) module can generate a clock, its frequency is determined by the delay unit of the clock oscillation loop circuit. The generated clock can be used as a clock source for the chip in standby; the external clock 32.768KHz will reach optimal chip standby power consumption when RK3568 chip in sleeps, and the PVTM module can also be turned off at this time.

- The external 32.768KHz clock can be obtained from PMIC or external RTC clock source. The 32.768KHz clock input pin of RK3568 is shown in the figure below:

| CLK32K_IN | / CLK32K_OUT0 | / PCIE30X2_BUTTONRSTn                          | / | GPIO0 B0 u | AD23 |

|-----------|---------------|------------------------------------------------|---|------------|------|

|           | Figure 2-2 RI | K3568 the 32.768KHz clock input pin in standby |   |            |      |

• The external 32.768kHz RTC clock parameters are shown in Table 2-2 below

| Parameters      |          | Spec     | - Description |                    |  |

|-----------------|----------|----------|---------------|--------------------|--|

| rarameters      | Min.     | Max.     | Unit          | Description        |  |

| Frequency       | 32.76    | 58000    | kHz           |                    |  |

| Frequency       | +/       | -30      | nnm           |                    |  |

| tolerance       | 17.      | -30      | ppm           |                    |  |

| Clock amplitude | 0.65*VDD | VDD+0.3V | V             | VDD:PMUIO2 voltage |  |

| Operating       | -20      | 80       | °C            |                    |  |

| temperature     | -20      | 80       | C             |                    |  |

| Duty Ratio      | 5        | 0        | %             |                    |  |

#### Table 2–2 RK3568 32.768KHz clock requirements

# Note

When using this function, the IOMUX pin must be set to CLK32K\_IN function, and the input amplitude must meet the power supply requirements of PMUIO2 Domain.

- RK3568 can provide working clocks to peripherals:

- REFCLK\_OUT: 24MHz clock output as default, which can be provided to Camera and other devices as working clock

- CLK32K\_OUT0: 32.768KHz clock output, which can be provided to WIFI, BT, PCIe and other devices as sleep or working clock

- CLK32K\_OUT1: 32.768KHz clock output, which can be provided to WIFI, BT, PCIe and other devices as sleep or working clock

- ETH0\_REFCLKO\_25M: 25MHz clock output, which can be provided to Ethernet PHY and other devices as working clock

- ETH1\_REFCLKO\_25M\_M0/ETH1\_REFCLKO\_25M\_M1: 25MHz clock output, which can be provided to Ethernet PHY and other devices as working clock

- CIF\_CLKOUT: 24MHz clock output by default, other frequency value can be obtained according to PLL frequency division, which can be provided to Camera and other devices as working clock

- CAM\_CLKOUT0: 24MHz clock output by default, other frequency points can be obtained according to PLL frequency division, which can be provided to Camera and other devices as working clock

- CAM\_CLKOUT1: 24MHz clock output by default, other frequency value can be obtained according to PLL frequency division, which can be provided to Camera and other devices as working clock

The IO Domains where the above clocks are located must match the IO level of connected peripherals. If they do not match, a level conversion circuit must be added.

Please evaluate whether they can meet the clock requirements of the peripheral device.

#### 2.1.2 Reset/watchdog/TSADC Circuit

The hardware reset signal of RK3568 is input through Pin AH27 (NPOR\_u), which must be controlled externally and is active at low level. In order to ensure the stability and normal operation of the chip, the minimum reset time required is 100 cycles of the 24MHz main clock, that is, at least 4us or more.

Pin AH27 (NPOR\_u) has to add a 100nF capacitor to eliminate jitter of the reset signal, enhance anti-interference ability, and prevent abnormal system reset caused by false triggering.

The pull-up power of the RESETn network must be consistent with the IO domain (PMUIO1) where the nPOR pin is located.

Figure 2-3 RK3568 reset input (RK809-5 solution)

Figure 2-4 RK3568 reset input (discrete power solution)

Note: The reset IC must be with open-drain output, and low level active.

- The RK3568 chip integrates a Watchdog Timer. When a reset signal is generated, a low level will be output through TSADC\_SHUT\_M0 or TSADC\_SHUT\_M1 pin, and then resets RK3568 by hardware.

- The RK3568 chip integrates two TSADC (Temperature-Sensor ADC) modules. When the temperature inside the chip exceeds the threshold, the internal TSHUT signal can be passed to the CRU module and reset RK3568 chip, or it can output low level through TSADC\_SHUT\_M0 or TSADC\_SHUT\_M1 pin to reset RK3568 by hardware. As shown in the figure above, the TSADC\_SHUT\_M0 network is connected to the RESETn network.

- RK3568 reset signal path diagram is as follows:

Figure 2-5 RK3568 the path of reset signal

• When the RESETB pin of RK809-5 is powered on for the first time, after all power supplies are powered on, RESETB will change from low level to high level (open drain output) after delaying the set time, to complete the power-on reset process; when RK809-5 is in working or sleep mode, if the RESETB pin is pulled low, RK809-5 will also be restarted. The restart power-on sequence is the same as the first time power-on.

#### 2.1.3 PMU Circuit

In order to meet the requirement of low power consumption products, RK3568 has designed a power management unit (PMU) to control and manage the internal power supply of the chip.

This module supports registers inside chip or PMUIO power domain IO control peripheral power circuit, *Copyright* © 2022 *Rockchip Electronics Co., Ltd.*

#### **RK3568 Hardware Design Guide**

realize power on and power off to other functional modules, and also support IO interrupt wake-up, so as to realize the chip's standby and wake-up functions.

#### 2.1.4 System Boot Sequence

The RK3568 chip supports multiple booting ways. After chip reset, the boot code integrated inside the chip will automatically boot in the following sequence:

- Serial Nor Flash (FSPI)

- Serial Nand Flash (FSPI)

- Nand Flash

- eMMC

- SDMMC0 Card

If there is no boot code in the above devices, you can download the system code to these devices through the USB3\_OTG0\_DP/USB3\_OTG0\_DM signal of the USB3.0 OTG0 interface.

#### 2.1.5 System Initialization Configuration Signal

There are two important signals in RK3568 will affect the system boot configuration, which need to be configured and kept stable before power-on. They are:

- FLASH\_VOL\_SEL pin (Pin AG25): hardware configuration VCCIO2 power domain IO driver voltage

- SDMMC0\_DET pin (Pin Y22): determine whether VCCIO3 power domain IO is SDMMC0 or JTAG function

After the system reset, the chip will configure the default power-on function of the corresponding module according to the input level of the two pins

- The IO drive voltage mode of RK3568 VCCIO2 power domain is configured by hardware by default. Because it belongs to FLASH power domain, it's used during system boots. Therefore, when the system is booting, the IO drive voltage mode must be set through the hardware configuration first instead of setting by register operation, as shown below:

- When VCCIO2 voltage is connected to 1.8V, FLASH\_VOL\_SEL must be high;

- When VCCIO2 voltage is connected to 3.3V, FLASH\_VOL\_SEL must be low;

- If the IO power supply is changed, the FLASH\_VOL\_SEL pin must be changed synchronously, they cannot be mismatch, otherwise the function will be abnormal or the chip may even be damaged.

Figure 2-6 RK3568 VCIO2 power supply and FLASH\_VOL\_SEL

The ARM JTAG function of RK3568 is reused with the SDMMC0 function, and the IOMUX function is switched through the SDMMC0 DET pin. Therefore, you have to finish configuration operate of this pin before power-on, otherwise the ARM JTAG function has no output that will affect the debugging during booting, no output from SDMMC0 will affect the boot function of SDMMC0.

| pera   | ting | g  | NOT.  | tage   | =1 | •8V,  | /3   | .3V   |   |      |     |           |   |       |     |    | 705        |

|--------|------|----|-------|--------|----|-------|------|-------|---|------|-----|-----------|---|-------|-----|----|------------|

| SDMMC0 |      | /  |       | _TX_M1 | 7  | UART6 |      | _     |   | PWM8 | _   |           | / | GPI01 | D5  | u  | J25<br>J24 |

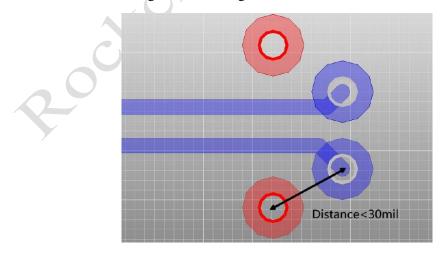

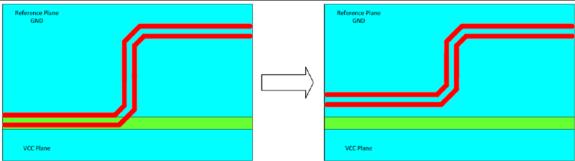

| SDMMC0 |      | /  |       | _RX_M1 | /  | UART6 |      |       |   | PWM9 | _M1 |           | / | GPI01 |     |    | H26        |