# RK3566 Hardware Design Guide

(Hardware Department)

|                            | Version:  | 1.1.0      |

|----------------------------|-----------|------------|

| Status:                    | Author:   | Daniel.Jin |

| [ ] Draft<br>[ ] Modifying | Date:     | 2022-02-06 |

| [√] Released               | Approver: | Reviewer   |

|                            | Date:     | 2022-02-06 |

Rockchip Electronics Co., Ltd.

# Disclaimer

This document is provided "status quo", Rockchip Electronics Co., Ltd. ("the company", the same below) does not make any statements, information and content of this document on the accuracy, reliability, completeness, marketability, or specific purpose and non-infringement provide any express or implied statement or guarantee. This document is only used as a reference for instructions.

Due to product version upgrades or other reasons, this document will be updated aperiodic. Unless otherwise agreed, this document is only used as a guide. All statements, information and suggestions in this document do not constitute any express or implied warranty.

# **Brand Statement**

"Rockchip" and "瑞芯微", "瑞芯"and other Rockchip trademarks are trademarks of Rockchip Electronics co., ltd., are exclusively owned by Rockchip Electronics Co., Ltd.

All other trademarks or registered trademarks mentioned in this document are owned by their respective owners.

# Copyright © 2022 Rockchip Electronics Co., Ltd.

Without the written permission of the company, any unit or individual shall not extract or copy part or all of the content of this document, shall not disseminate it in any form.

Rockchip Electronics Co., Ltd.Add:No. 18, A District, No.89, Soft-ware Boulevard Fuzhou, Fujian, PRCWeb:www.rock-chips.comCustomer service tel:+86-4007-700-590Customer service fax:+86-591-83951833Customer service e-mail:fae@rock-chips.com

# **Revision History**

The revision history accumulates instructions for each update of the document and the latest version includes updates of all previous versions.

| Version | Author    | <b>Revision Date</b> | Revision Description             |  |

|---------|-----------|----------------------|----------------------------------|--|

| V1.0.0  | Daniel. J | 2021.06.03           | 1 <sup>st</sup> Released Version |  |

| V1.1.0  | Daniel. J | 2022.02.06           | Modified some descriptions       |  |

|         |           |                      |                                  |  |

|         |           |                      |                                  |  |

|         |           |                      |                                  |  |

# Preface

# Overview

This document mainly describes the key points of hardware design and notices for RK3566 processor, aiming to help RK customers shorten the product design cycle, improving the product design stability and reducing the failure rate. Please refer to the requirements in this guide to do the hardware design, and suggest to use the relevant core templates released by Rockchip. If you need to make changes for specific reasons, please adhere to the design rules of high-speed-digital-circuit and RK Schematic & PCB checklist requirements.

# Chip Type

This document is suitable for : RK3566

# **Applicable Object**

This document is mainly suitable for below:

- Product Hardware Development Engineers

- Field Application Engineers

- Test Engineers

# **Related Reference Documents**

- RK3566\_PinOut: Pin list, Ball map, GPIO information, Pin delay, Usage of unused pins;

- Rockchip\_RK3566\_High\_Speed\_PCB\_Design\_Guide: Design guide of high speed signals, Layout requirements and suggestions;

- RK356X Power Consumption Test Report: Reference data about power consumption;

- Rockchip\_RK3566\_IO\_Power\_Domain\_Checklist: Checklist of THE IO power domain;

- Rockchip\_RK3566\_Schematic\_and\_PCB\_Review\_Checklist: schematic diagram, PCB check table;

- Rockchip\_RK3566\_Hardware\_Design\_Guide: Hardware Design Guide;

# Abbreviation

| Abbreviation         | English Interpretation                    | Chinese Interpretation                    |  |  |

|----------------------|-------------------------------------------|-------------------------------------------|--|--|

| ARM/CPU              | ARM based Central Processing Unit         | 基于 ARM 的中央处理器                             |  |  |

| Acodec               | Audio Codec                               | 音频编解码器                                    |  |  |

| CEC                  | Consumer Electronics Control              | 消费电子控制                                    |  |  |

| CIF                  | Camera Input Format                       | 相机并行接口                                    |  |  |

| CSI                  | Camera Serial Interface                   | 相机串行接口                                    |  |  |

| DC/DC                | Direct Current-Direct Current Convertor   | 直流/直流转换器                                  |  |  |

| DDR                  | Double Data Rate                          | 双倍速率同步动态随机存储器                             |  |  |

| DP                   | Display Port                              | 显示接口                                      |  |  |

| DSI                  | Display Serial Interface                  | 显示串行接口                                    |  |  |

| EBC                  | E-book Controller                         | 电子书控制器                                    |  |  |

| eDP                  | Embedded Display Port                     | 嵌入式数码音视频传输接口                              |  |  |

| eMMC                 | Embedded Multi Media Card                 | 内嵌式多媒体存储卡                                 |  |  |

| ESD                  | Electro-Static Discharge                  | 静电释放                                      |  |  |

| ESR                  | Equivalent Series Resistance              | 等效电阻                                      |  |  |

| FSPI                 | Flexible Serial Peripheral Interface      | 灵活串行外设接口                                  |  |  |

| GPU                  | Graphics Processing Unit                  | 图形处理器                                     |  |  |

| GMAC                 | Gigabit Media Access Controller           | 千兆媒体访问控制器                                 |  |  |

| HDMI                 | High-Definition Multimedia Interface      | 高清晰度多媒体(接口)                               |  |  |

| I <sup>2</sup> C/I2C | Inter-Integrated Circuit                  | 内部整合电路(线式串行通讯总线)                          |  |  |

| I2S                  | Inter-IC Sound                            | 集成电路内置音频总线                                |  |  |

| ISP                  | Image Signal Processing                   | 图像信号处理                                    |  |  |

| JTAG                 | Joint Test Action Group                   | 联合测试行为组织定义的一种国际标<br>准测试协议(IEEE 1149.1 兼容) |  |  |

| LDO                  | Low Drop Out Linear Regulator             | 低压差线性稳压器                                  |  |  |

| LVDS                 | Low-Voltage Differential Signaling        | 低电压差分信号(接口)                               |  |  |

| MAC                  | Media Access Control                      | 以太网媒体接入控制器                                |  |  |

| MIPI                 | Mobile Industry Processor Interface       | 移动产业处理器(接口)                               |  |  |

| NPU                  | Netural-network Processing Unit           | 神经网络处理器                                   |  |  |

| PCIe                 | Peripheral Component Interconnect Express | 外设组件互联标准                                  |  |  |

| PDM                  | Pulse Density Modulation                  | 脉冲密度调制 (接口)                               |  |  |

| PMIC                 | Power Management IC                       | 电源管理芯片                                    |  |  |

| PMU                  | Power Management Unit                     | 电源管理单元                                    |  |  |

| PWM                  | Pulse Width Modulation                    | 脉冲宽度调制                                    |  |  |

Acronym includes the abbreviations of commonly used phrases in this document:

| Rockchip | Rockchip Electronics Co., Ltd.                                   | 瑞芯微电子股份有限公司   |  |

|----------|------------------------------------------------------------------|---------------|--|

| RGMII    | Reduced Gigabit Media Independent Interface                      | 简化千兆媒体独立接口    |  |

| RMII     | Reduced Media Independent Interface                              | 简化媒体独立接口      |  |

| SARADC   | Successive Approximation Register<br>Analog to Digital Converter | 逐次逼近寄存器型模数转换器 |  |

| SD Card  | Secure Digital Memory Card                                       | 安全数码卡         |  |

| SDIO     | Secure Digital Input and Output Card                             | 安全数字输入/输出卡    |  |

| SDMMC    | Secure Digital Multi Media Card                                  | 安全数字多媒体存储卡    |  |

| SPI/FSPI | (Flexible)Serial Peripheral Interface                            | (灵活)串行外设(接口)  |  |

| SPDIF    | Sony/Philips Digital Interface Format                            | 索尼/飞利浦数字音频接口  |  |

| SPI      | Serial Peripheral Interface                                      | 串行外设接口        |  |

| TF Card  | Micro SD Card(Trans-flash Card)                                  | 外置记忆卡         |  |

| TSADC    | Temperature Sensing Analog to Digital<br>Converter               | 温度感应模数转换器     |  |

| VOP      | Video Output Processor                                           | 视频输出处理器       |  |

| VPU      | Video Processing Unit                                            | 视频处理器         |  |

| UART     | Universal Asynchronous<br>Receiver/Transmitter                   | 通用异步收发传输器     |  |

| USB      | Universal Serial Bus                                             | 通用串行总线        |  |

# Contents

| 1 | INT  | RODUCTION                                    | 13 |

|---|------|----------------------------------------------|----|

|   | 1.1  | OVERVIEW                                     | 13 |

|   | 1.2  | BLOCK DIAGRAM                                | 13 |

|   | 1.3  | APPLICATION BLOCK DIAGRAM                    | 14 |

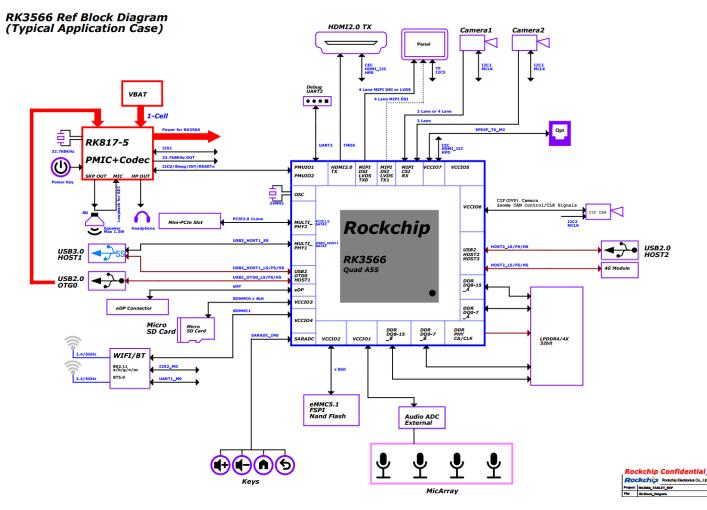

|   | 1.3. | 1 RK817-5 Application Block Diagram          | 14 |

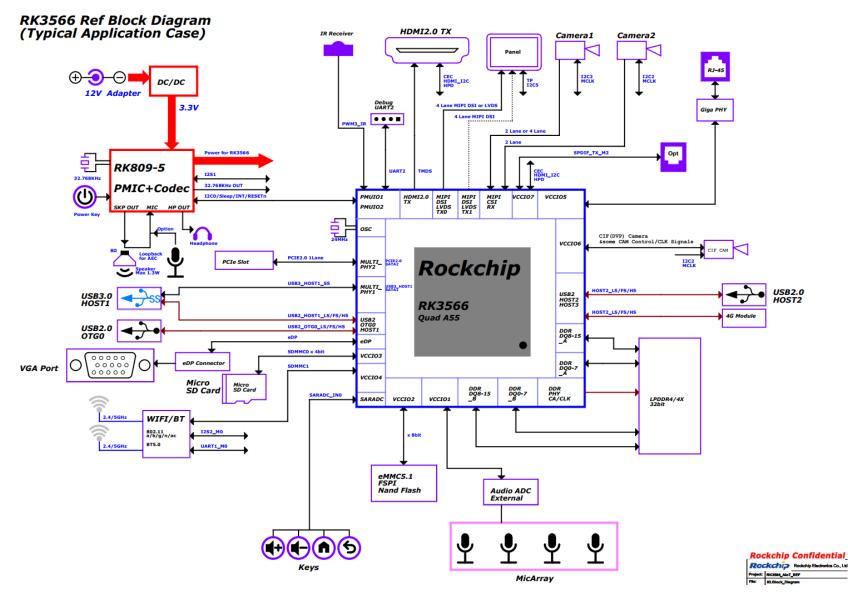

|   | 1.3. | 2 RK809-5 Application Block Diagram          | 15 |

| 2 | HA   | RDWARE DESIGN RECOMMENDATION                 | 16 |

|   | 2.1  | MINIMUM SYSTEM DESIGN                        | 16 |

|   | 2.1. | 1 Clock Circuit                              | 16 |

|   | 2.1. | 2 Reset Circuit                              | 17 |

|   | 2.1. | 3 Watchdog/TSADC Circuit                     | 18 |

|   | 2.1. | 4 PMU Circuit                                | 18 |

|   | 2.1. | 5 System Boot Sequence                       | 18 |

|   | 2.1. | 6 System Initialization Configuration Signal | 19 |

|   | 2.1. | 7 JTAG Debug Circuit                         | 20 |

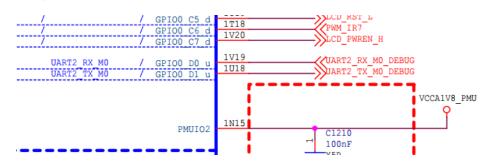

|   | 2.1. | 8 UART Debug Circuit                         | 21 |

|   | 2.1. | 9 DDR Circuit                                | 21 |

|   | 2.1. | 10 eMMC Circuit                              | 26 |

|   | 2.1. | 11 Nand Flash Circuit Design                 | 28 |

|   | 2.1. | 12 FSPI Flash Circuit                        | 29 |

|   | 2.1. | 13 GPIO Circuit                              | 30 |

|   | 2.2  | Power Design                                 | 33 |

|   | 2.2. | 1 Minimum System Power Introduction          | 33 |

|   | 2.2. | 2 Power Design Recommendation                | 34 |

|   | 2.2. | 3 Power peak Ammeter                         | 41 |

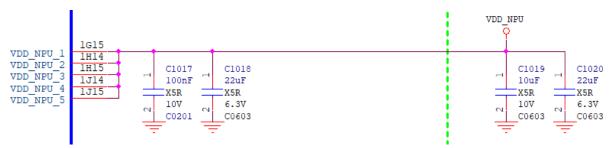

|   | 2.2. | 4 RK817-5 Scheme Introduction                | 42 |

|   | 2.2. | 5 RK809-5 Scheme Introduction                | 47 |

|   | 2.2. | 6 Over Temperature Protection Circuit        | 51 |

|   | 2.2. | 7 PMIC SLEEP Standby Control Circuit         | 51 |

|   | 2.3  | FUNCTION INTERFACE CIRCUIT DESIGN            | 52 |

|   | 2.3. | 1 SDMMC Memory Card Circuit                  | 52 |

|   | 2.3. | 2 USB Circuit                                | 54 |

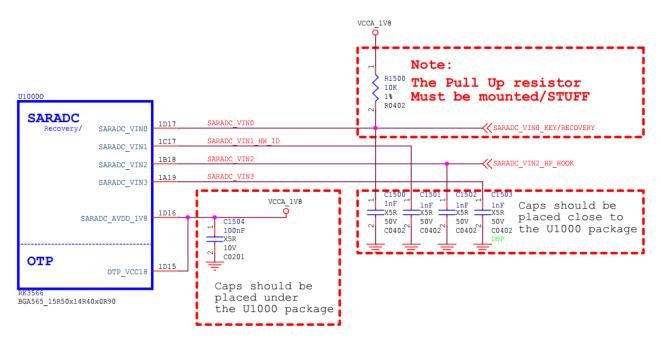

|   | 2.3. | 3 SARADC Circuit                             | 59 |

|   | 2.3. | 4 OTP Circuit                                | 60 |

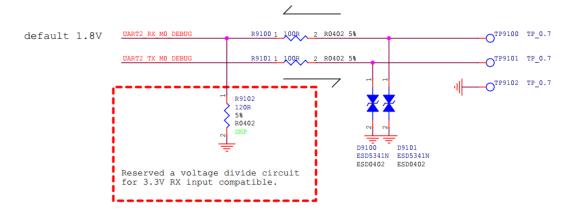

|   | 2.3. | 5 UART and Debug UART Circuit                | 60 |

|   | 2.3. | 6 I2C Circuit                                | 63 |

|   | 2.3. | 7 PWM Circuit                                | 64 |

|   | 2.3. | 8 SPI Circuit                                | 65 |

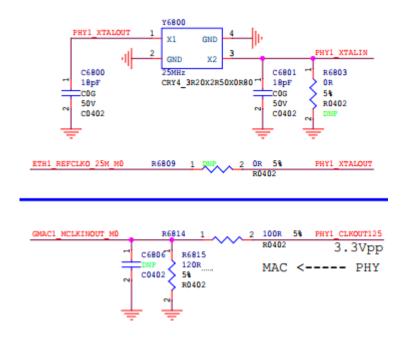

|   | 2.3. | 9 Ethernet Interface                         | 65 |

|   | 2.4  | AUDIO RELATED CIRCUIT DESIGN                 | 69 |

|   | 2.4.           | I2S1 Digital Audio Interface                              | . 69 |

|---|----------------|-----------------------------------------------------------|------|

|   | 2.4.2          | 2 I2S2 Digital Audio Interface                            | . 70 |

|   | 2.4.3          | I2S3 Digital Audio Interface                              | . 71 |

|   | 2.4.4          | PDM Digital Audio Interface                               | . 71 |

|   | 2.4.5          | SPDIF Digital Audio Interface                             | . 72 |

|   | 2.4.6          | Codec and Analog Audio Interface                          | . 73 |

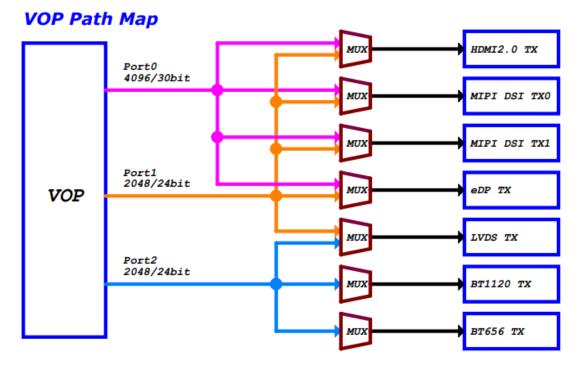

|   | 2.5            | VIDEO OUTPUT INTERFACE DESIGN                             | . 77 |

|   | 2.5.           | MIPI-DSI Output                                           | . 77 |

|   | 2.5.2          | 2 LVDS Output                                             | . 78 |

|   | 2.5.3          | eDP Output                                                | . 79 |

|   | 2.5.4          | HDMI2.0 TX Output                                         | . 80 |

|   | 2.5.5          | 5 BT1120 Output                                           | . 81 |

|   | 2.5.6          | 5 BT656 Output                                            | . 82 |

|   | 2.5.7          | 7 EBC Output                                              | . 82 |

|   | 2.5.8          | Design Attention to LCD Screen and Touch Screen           | . 82 |

|   | 2.6            | VIDEO INPUT INTERFACE DESIGN                              | . 83 |

|   | 2.6.           | MIPI-CSI Interface                                        | . 83 |

|   | 2.6.2          | 2 DVP (CIF) Parallel Port Camera Input                    | . 85 |

|   | 2.7            | COMBINED HIGH-SPEED INTERFACE DESIGN (MULTI PHY)          |      |

|   | 2.7.1          | SATA3.0 High Speed Interface                              | . 88 |

|   | 2.7.2          | PCIe 2.0 High Speed Interface                             | . 88 |

| 3 | THI            | ERMAL DESIGN RECOMMENDATION                               | . 90 |

|   | 3.1            | THERMAL SIMULATION RESULT                                 | . 90 |

|   | 3.1.           | Result Summaries                                          | . 90 |

|   | 3.1.2          | PCB Information                                           | . 90 |

|   | 3.1.3          | 3 Terminology                                             | . 90 |

|   | 3.2            | INNER SOC THERMAL CONTROL METHOD                          |      |

|   | 3.2.1          |                                                           |      |

|   | 3.2.2          |                                                           |      |

|   | 3.3            | SUGGESTIONS FOR THERMAL DESIGN OF CIRCUITS AND PCB LAYOUT |      |

| 4 | ESD            | /EMI PROTECTION DESIGN                                    |      |

|   | 4.1            | OVERVIEW                                                  |      |

|   | 4.2            | TERMINOLOGY EXPLAIN                                       |      |

|   | 4.3            | SUGGESTIONS FOR ESD PROTECTION                            |      |

|   | 4.4            | SUGGESTIONS FOR EMI PROTECTION                            |      |

| 5 |                | LDING PROCESS                                             |      |

|   | 5.1            | OVERVIEW                                                  |      |

|   | 5.2            | TERMINOLOGY EXPLAIN                                       |      |

|   | 5.3            | REFLOW SOLDER REQUIREMENT                                 |      |

|   | 5.3.1          | Solder Paste Composition and Operation Requirement        | . 97 |

|   |                |                                                           |      |

|   | 5.3.2<br>5.3.3 |                                                           | . 97 |

| 6 | PAC   | CKAGING AND STORAGE CONDITION       | 100 |

|---|-------|-------------------------------------|-----|

|   | 6.1   | OVERVIEW                            | 100 |

|   | 6.2   | TERMINOLOGY EXPLAIN                 | 100 |

|   | 6.3   | DRY VACUUM PACKAGING                | 100 |

|   | 6.4   | STORAGE OF PRODUCT                  | 101 |

|   | 6.4.  | 1 Storage Environment               | 101 |

|   | 6.4.2 | 2 Exposure Time                     | 101 |

|   | 6.5   | USAGE OF MOISTURE SENSITIVE PRODUCT | 101 |

# **List of Figures**

| Figure 1-1 RK3566 Block Diagram                                                    |    |

|------------------------------------------------------------------------------------|----|

| Figure 1-2 RK3566 RK817-5 Application Block Diagram                                | 14 |

| Figure 1-3 RK3566 RK809-5 Application Block Diagram                                |    |

| Figure 2-1 RK3566 Crystal Implementation                                           | 16 |

| Figure 2-2 RK3566 Reset Input                                                      |    |

| Figure 2-3 Correspondence Between RK3566 FLASH_VOL_SEL Pin Level And VCCIO2 Status | 19 |

| Figure 2-4 RK3566 SDMMC0/JTAG Reused Control Pin                                   |    |

| Figure 2-5 RK3566 JTAG Connection Circuit In SWD Mode                              |    |

| Figure 2-6 RK3566 LPDDR3 Topological Structure                                     | 22 |

| Figure 2-7 DQ[7:0] connection description of LPDDR3 particle                       |    |

| Figure 2-8 Different DDR particles correspond to VDDQ/VDDQL supply voltage         |    |

| Figure 2-9 DDR3 SDRAM's power-on sequence                                          |    |

| Figure 2-10 LPDDR3 SDRAM's power-on sequence                                       | 24 |

| Figure 2-11 DDR4 SDRAM's power-on sequence                                         | 24 |

| Figure 2-12 LPDDR4 SDRAM's Power-on Sequence                                       | 25 |

| Figure 2-13 Description of DDR RZQ Connection                                      |    |

| Figure 2-14 eMMC power up/down sequence                                            |    |

| Figure 2-15 Nand Flash power-on/down sequence                                      |    |

| Figure 2-16 RK3566 Standby Circuit Solution                                        |    |

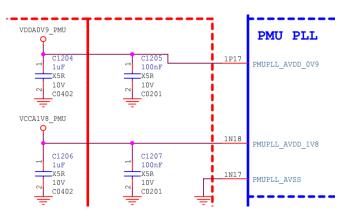

| Figure 2-17 RK3566 PMU PLL power                                                   |    |

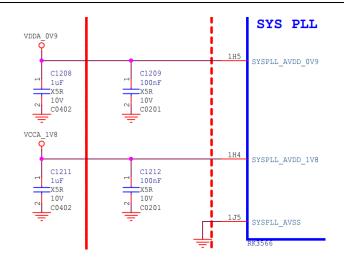

| Figure 2-18 RK3566 SYS PLL power                                                   |    |

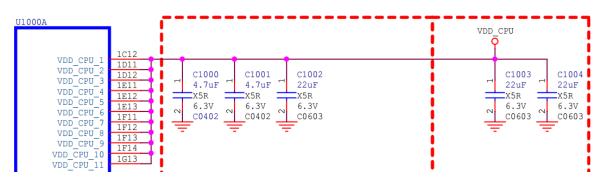

| Figure 2-19 RK3566 VDD_CPU Power and Decoupling                                    | 36 |

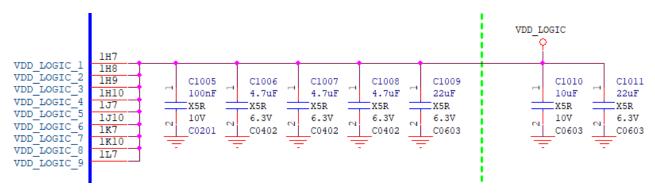

| Figure 2-20 RK3566 LOGIC Power and Decoupling                                      |    |

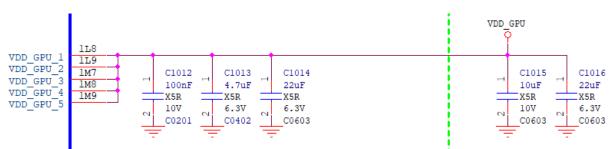

| Figure 2-21 RK3566 VDD_GPU power and decoupling                                    |    |

| Figure 2-22 RK3566 VDD_NPU power and decoupling                                    |    |

| Figure 2-23 RK3566 power's remote feedback compensation                            | 38 |

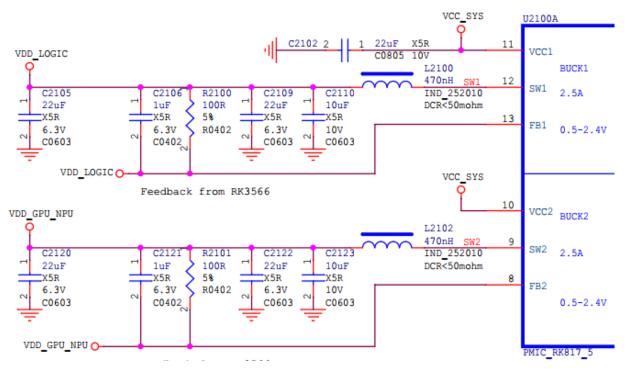

| Figure 2-24 RK3566 VCC_DDR power                                                   | 39 |

| Figure 2-25 RK3566 DDR power and decoupling in DDR3/DDR3L/DDR4/LPDDR3/LPDDR4       | 39 |

| Figure 2-26 RK3566 DDR power and decoupling in LPDDR4X                             | 40 |

| Figure 2-27 RK3566 0.9V related power supply design                                |    |

| Figure 2-28 RK3566 7.8V related power supply design                                | 41 |

| Figure 2-29 RK817-5 block diagram                                                  |    |

| Figure 2-30 RK3566+RK817-5 Typical application power tree                          |    |

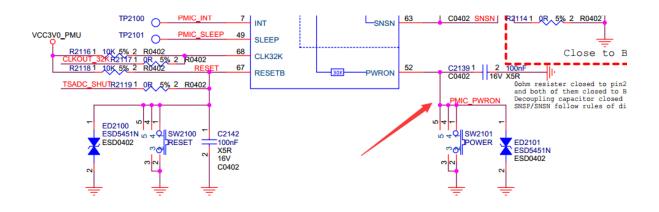

| Figure 2-31 RK817-5 PWRON pin                                                      |    |

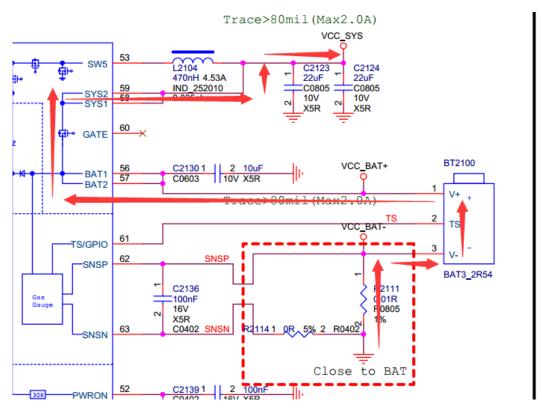

| Figure 2-32 Rk817-5 Battery discharge path                                         |    |

| Figure 2-33 RK809-5 block diagram                                                  |    |

| Figure 2-34 RK3566+RK809-5 Typical application power tree                          | 49 |

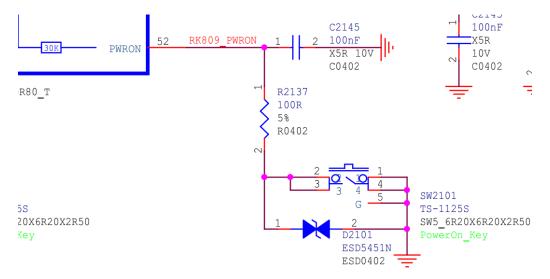

| Figure 2-35 RK809-5 PWRON pin                                                      | 50 |

| Figure 2-36 RK3566 TSADC_SHUT Over-temperature protection output                   |    |

| Figure 2-37 RK3566 PMIC_SLEEP output                                               |    |

| Figure 2-38 RK3566 PMIC_SLEEP input                                                |    |

| Figure 2-39 RK3566 SDMMC0 module                                                   |    |

| Figure 2-40 RK3566 WIFI/BT connection diagram                                      |    |

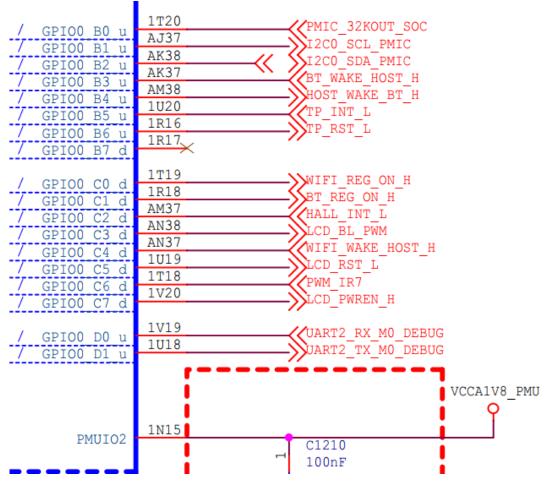

| Figure 2-41 RK3566 WIFI/BT control signal connection diagram                       | 54 |

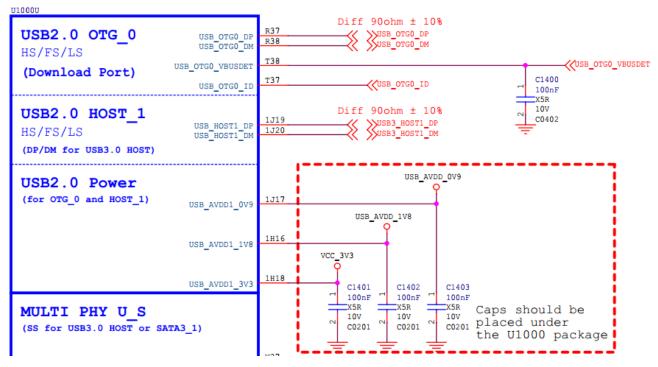

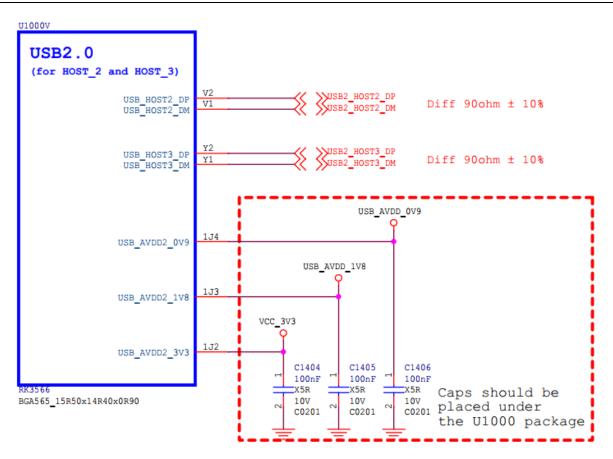

| Figure 2-42 RK3566 USB2.0 OTG/HOST1 module                                         |    |

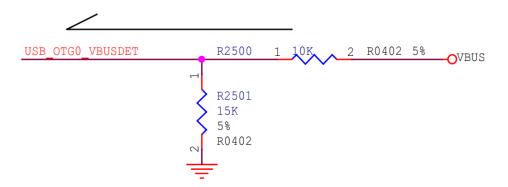

| Figure 2-43 RK3566 USB2.0 OTG VBUSDET voltage divider circuit                      |    |

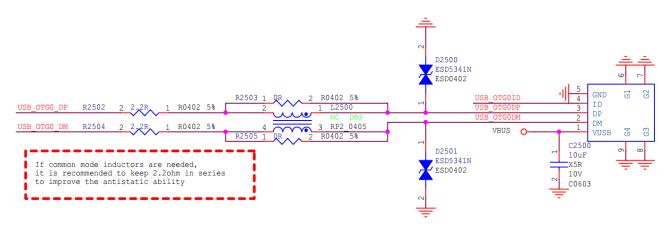

| Figure 2-44 RK3566 USB2.0 OTG signal circuit protection                            | 56 |

| Figure 2-45 RK3566 USB2.0 HOST2/HOST3 module                                       |    |

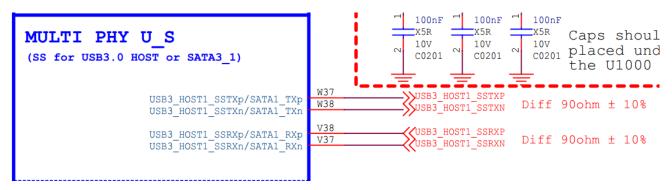

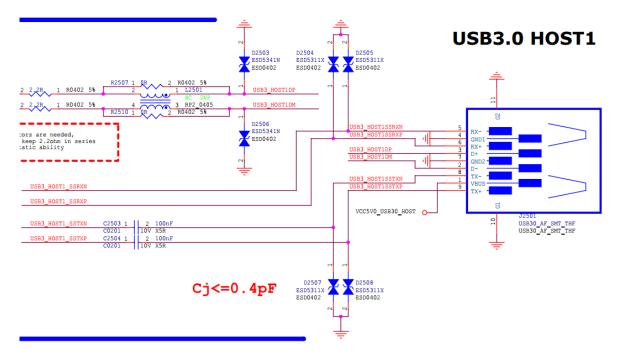

| Figure 2-46 RK3566 USB3.0 module                                                   |    |

| Figure 2-47 RK3566 USB3.0 signal circuit protection                                |    |

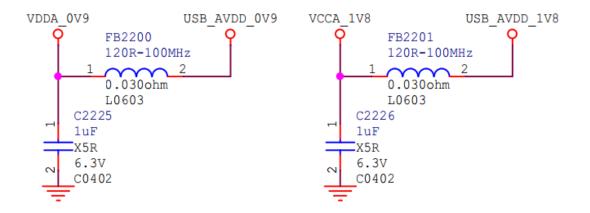

| Figure 2-48 RK3566 USB controller power supply design                              |    |

| Figure 2-49 RK3566 SAR-ADC module                                                  |    |

| Figure 2-50 RK3566 UART2 debug points                                              |    |

| Figure 2-51 RK3566 UART2 interface protection circuit                              |    |

| Figure 2-52 RK3566 serial port configuration                                       |    |

| Figure 2-53 RK3566 GMAC Clock circuit                                              |    |

| Figure 2-54 RK3566 RGMII RMII signal correspondence                                |    |

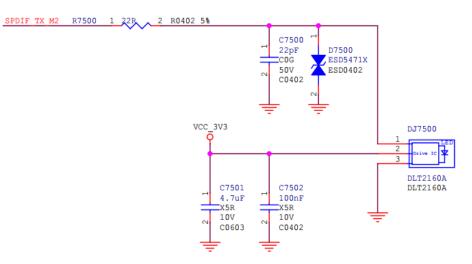

| Figure 2-55 RK3566 SPDIF optical fiber interface circuit                           |    |

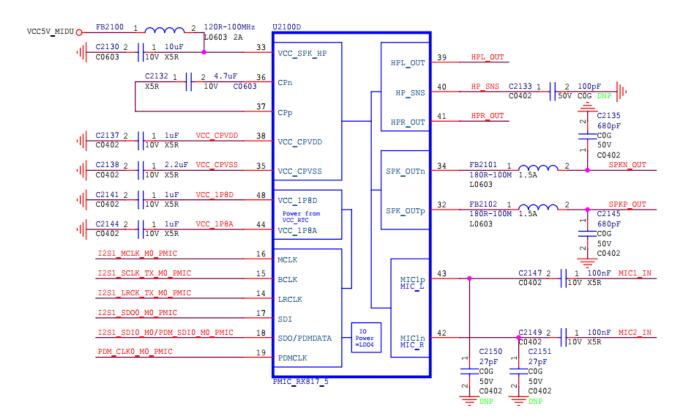

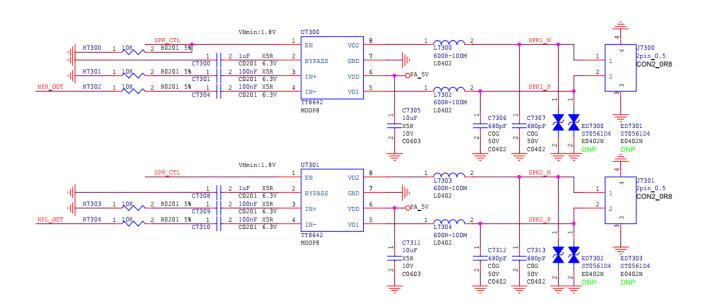

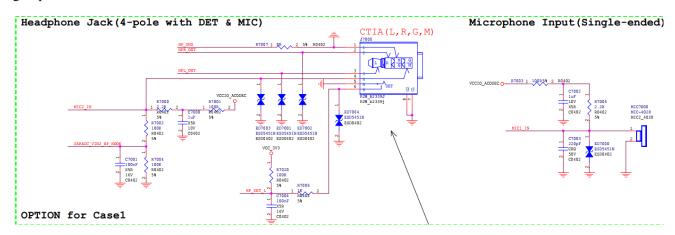

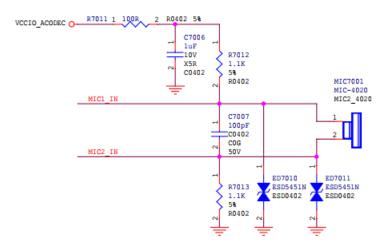

| Figure 2-56 RK817-5 Codec circuit                                                                | 73   |

|--------------------------------------------------------------------------------------------------|------|

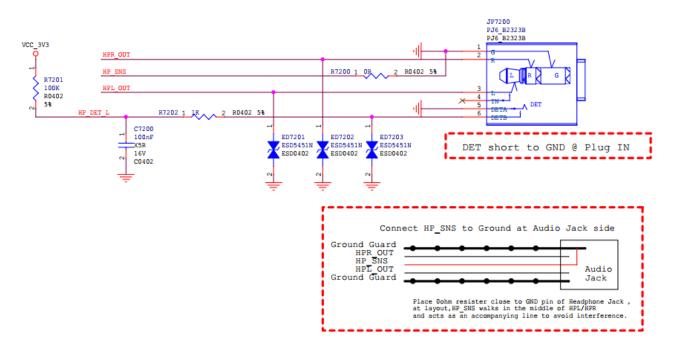

| Figure 2-57 RK817-5 Headphone circuit                                                            |      |

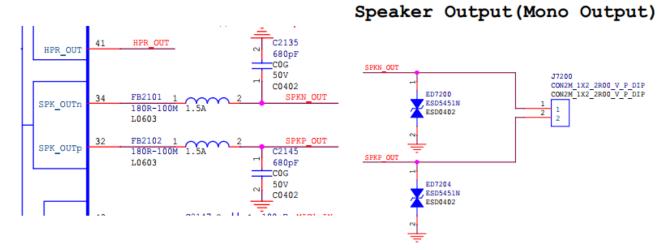

| Figure 2-58 RK817-5 Speaker circuit                                                              |      |

| Figure 2-59 RK817-5 external analog power amplifier diagram                                      |      |

| Figure 2-60 RK817-5 external four-segment earphone and single-ended microphone schematic diagram |      |

| Figure 2-61 RK817-5 external differential microphone schematic diagram                           |      |

| Figure 2-62 RK3566 video output interface path schematic diagram                                 |      |

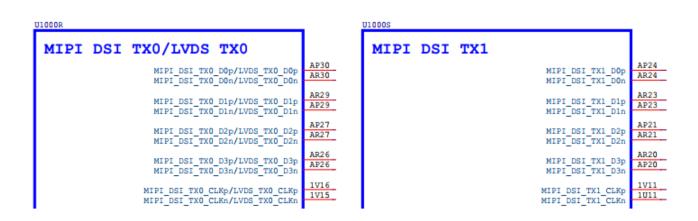

| Figure 2-63 RK3566 MIPI-DSI0/DSI1 and LVDS0 interface                                            |      |

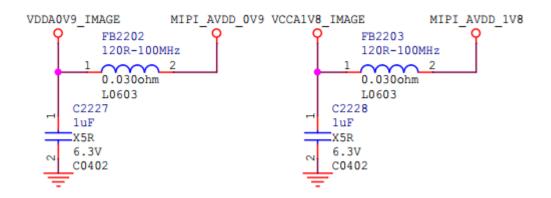

| Figure 2-64 RK3566 MIPI-CSI power supply connected with magnetic beads in series                 |      |

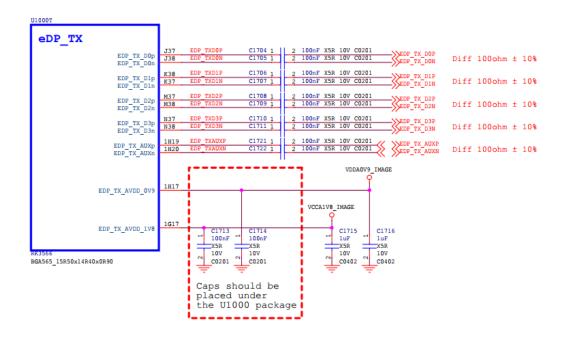

| Figure 2-65 RK3566 eDP interface                                                                 |      |

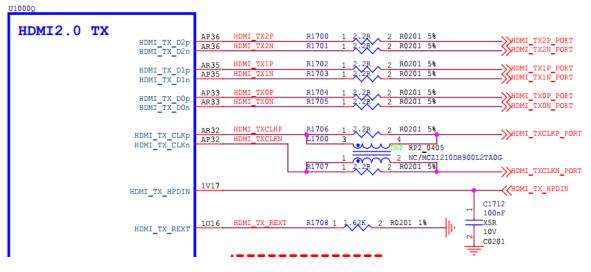

| Figure 2-66 RK3566 HDMI interface                                                                |      |

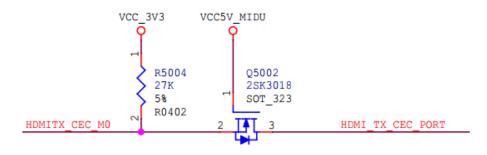

| Figure 2-67 RK3566 HDMI CEC anti-backflow circuit                                                | . 80 |

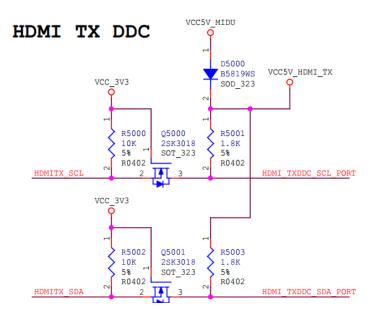

| Figure 2-68 RK3566 HDMI I2C level conversion circuit                                             |      |

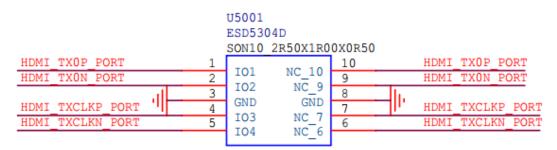

| Figure 2-69 RK3566 HDMI signal ESD protection                                                    |      |

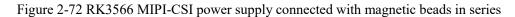

| Figure 2-70 RK3566 MIPI-CSI module                                                               |      |

| Figure 2-71 RK3566 MIPI-CSI working mode and data/clock distribution                             | . 84 |

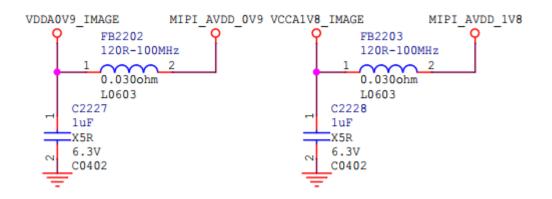

| Figure 2-72 RK3566 MIPI-CSI power supply connected with magnetic beads in series                 | . 84 |

| Figure 2-73 RK3566 DVP (CIF) parallel port camera signal correspondence table                    | 86   |

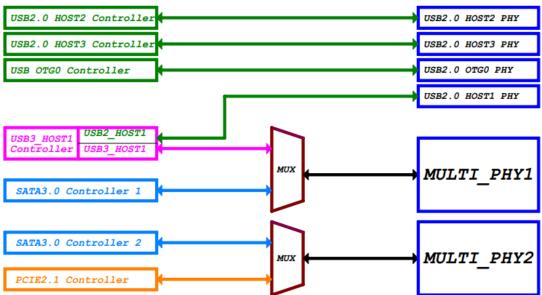

| Figure 2-74 RK3566 MULTI PHY path topology diagram                                               |      |

| Figure 2-75 RK3566 MULTI PHY signal and power                                                    |      |

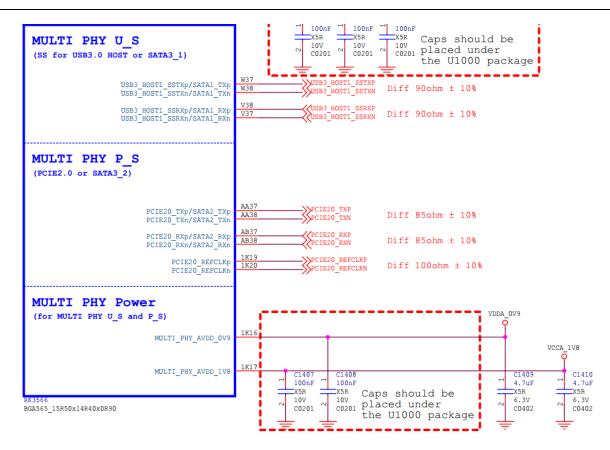

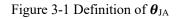

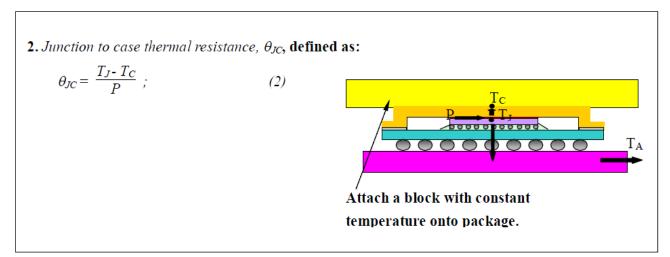

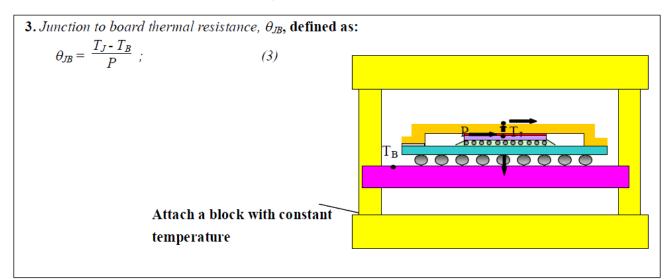

| Figure 3-1 Definition of $\boldsymbol{\theta}_{JA}$                                              | 91   |

| Figure 3-2 Definition of $\boldsymbol{\theta}_{\rm JC}$                                          |      |

| Figure 3-3 Definition of $\boldsymbol{\theta}_{\text{JB}}$                                       | 91   |

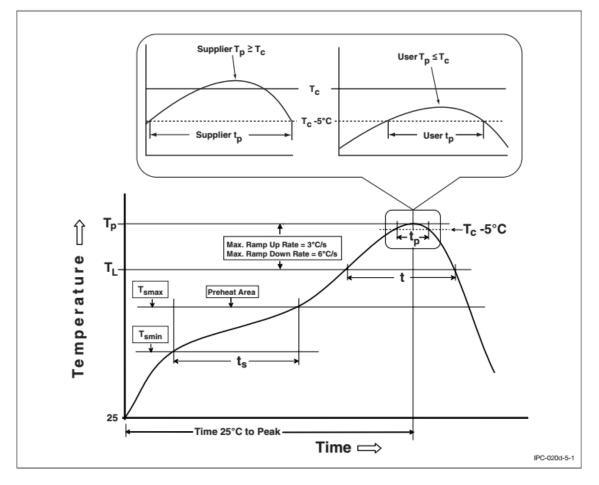

| Figure 5-1 Classification of Reflow Soldering Curves                                             | 98   |

| Figure 5-2 Heat Resistance Standard of Lead-free Process Device Package                          | 98   |

| Figure 5-3 Lead-free Reflow Soldering Process Curve                                              | 98   |

| Figure 6-1 Dry Vacuum Packaging for Chip 1                                                       | 100  |

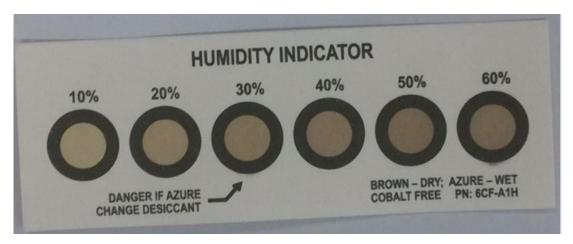

| Figure 6-2 Six-point Humidity Card 1                                                             |      |

# **List of Tables**

| Table 2-1 RK3566 24mhz Digital Clock Source                                                        | 17  |

|----------------------------------------------------------------------------------------------------|-----|

| Table 2-1 RK3566 32.768khz Clock Requirement                                                       | 17  |

| Table 2-3 RK3566 System Initialization Configuration Signal Description                            |     |

| Table 2-4 RK3568 JTAG debug interface signal                                                       |     |

| Table 2-5 RK3566 eMMC Interface Design                                                             |     |

| Table 2-6 RK3566 Nand Flash interface design                                                       |     |

| Table 2-7 RK3566 FSPI Interface Design                                                             |     |

| Table 2-8 RK3566 GPIO power pin description                                                        | 31  |

| Table 2-9 RK3566 power requirement                                                                 |     |

| Table 2-10 RK3566 internal PLL Introduction                                                        |     |

| Table 2-10 RK3566 SDMMC Interface Design                                                           |     |

| Table 2-12 RK3566 SDIO interface design                                                            |     |

| Table 2-12 RK3566 USB2.0 interface design                                                          |     |

| Table 2-19 RK3566 SARADC interface design                                                          |     |

| Table 2-15 RK3566 UART interface distribution                                                      |     |

| Table 2-16 RK3566 I2C interface distribution                                                       |     |

| Table 2-10 RK3566 PWM interface distribution                                                       |     |

| Table 2-17 RK3500 F with interface distribution       Table 2-18 RK3566 SPI interface distribution |     |

| Table 2-19 RK3566 RGMII/GMII interface design                                                      |     |

| Table 2-10 RK3566 I2S1 interface design                                                            |     |

| Table 2-20 RK3566 I2S1 interface design       Table 2-21 RK3566 I2S2 interface design              |     |

| Table 2-22 RK3566 I2S2 interface design       Table 2-22 RK3566 I2S3 interface design              |     |

| Table 2-23 RK3566 PDM interface design                                                             |     |

| Table 2-23 RK3566 SPDIF interface design                                                           |     |

| Table 2-25 Correspondence between RK3566 audio application scenarios and drawings                  |     |

| Table 2-26 RK3566 MIPI-DSI interface design                                                        |     |

| Table 2-27 RK3566 LVDS interface design                                                            |     |

| Table 2-28 RK3566 eDP interface design                                                             |     |

| Table 2-29 RK3566 HDMI interface design                                                            |     |

| Table 2-30 RK3566 BT1120 output signal description                                                 |     |

| Table 2-31 RK3566 BT656 output signal description                                                  |     |

| Table 2-32 RK3566 EBC output signal description                                                    |     |

| Table 2-33 RK3566 MIPI-CSI interface design                                                        |     |

| Table 2-34 RK3566 DVP (CIF) interface design                                                       |     |

| Table 2-35 RK3566 MULTI PHY configuration table                                                    |     |

| Table 2-36 RK3566 SATA interface design                                                            |     |

| Table 2-37 RK3566 PCIe interface design                                                            |     |

| Table 3-1 RK3566 thermal resistance simulation results                                             |     |

| Table 3-2 PCB structure of RK3566 thermal resistance simulation                                    | 90  |

| Table 5-1 SMT Curve Parameters.                                                                    |     |

| Table 6-1 Reference Table of Exposure Time (MSL)                                                   | 101 |

| Table 6-2 RK3566 Re-bake Reference Table.                                                          | 102 |

|                                                                                                    | 102 |

# **1** Introduction

# 1.1 Overview

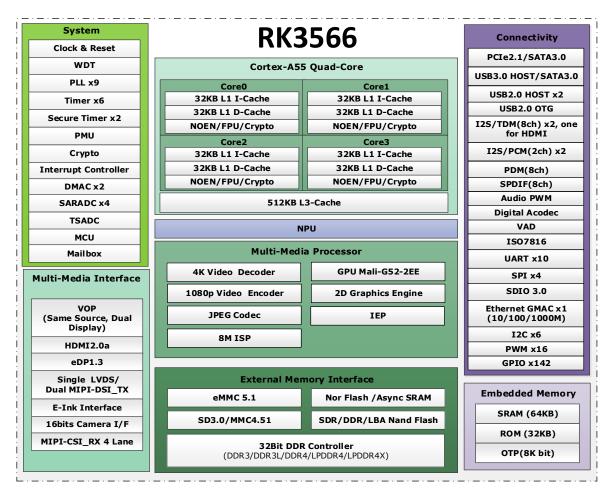

RK3566 is a high-performance, low-power, quad-core application processor chip, designed for personal mobile Internet devices and AIoT devices. It can be widely used in Android /Linux applications such as tablets, education tablets, speakers with screen, dictionary pens, cloud terminals, video conferencing systems. It can also be applied to consumer-grade or lightweight AI application scenarios with screens.

Many embedded powerful hardware engines are provided to optimize performance for highend application. RK3566 supports almost full-format H.264 decoder by 4K@60fps, H.265 decoder by 4K@60fps, also support H.264/H.265 encoder by 1080p@60fps, high-quality JPEG encoder/decoder.

RK3566 has an embedded 3D GPU, which is fully compatible with OpenGL ES1.1/2.0/3.2、 OpenCL 2.0 and Vulkan 1.0. The special MMU 2D hardware engine can maximize the display performance and provide smooth operation.

The embedded NPU supports INT8/INT16 hybrid operations. In addition, with its strong compatibility, you can easily transform network models based on frameworks such as TensorFlow/MXNet/PyTorch/Caffe.

RK3566 has a high-performance memory interface (DDR3/DDR3L/DDR4/LPDDR3/LPDDR4/LPDDR4X) to provide the memory bandwidth required in high-performance scenarios.

# **1.2 Block Diagram**

Figure 1-1 RK3566 Block Diagram

# **1.3** Application Block Diagram

# 1.3.1 RK817-5 Application Block Diagram

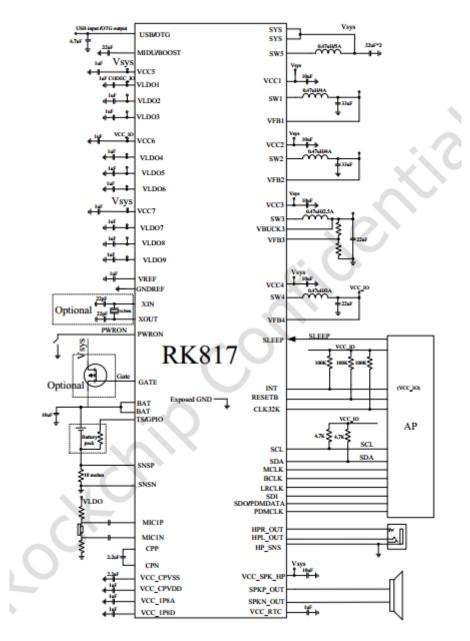

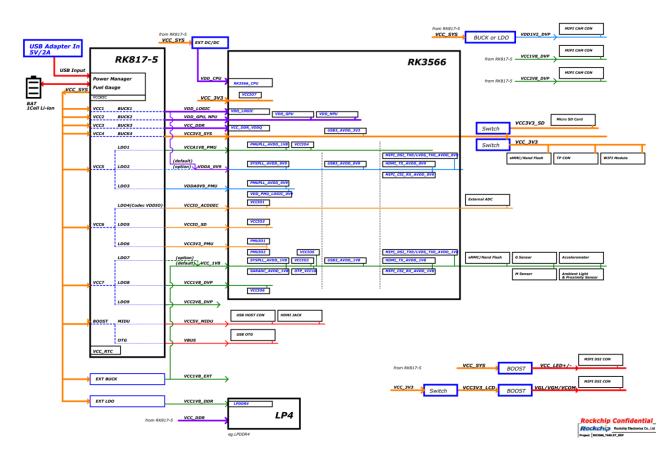

Figure 1-2 RK3566 RK817-5 Application Block Diagram

# 1.3.2 RK809-5 Application Block Diagram

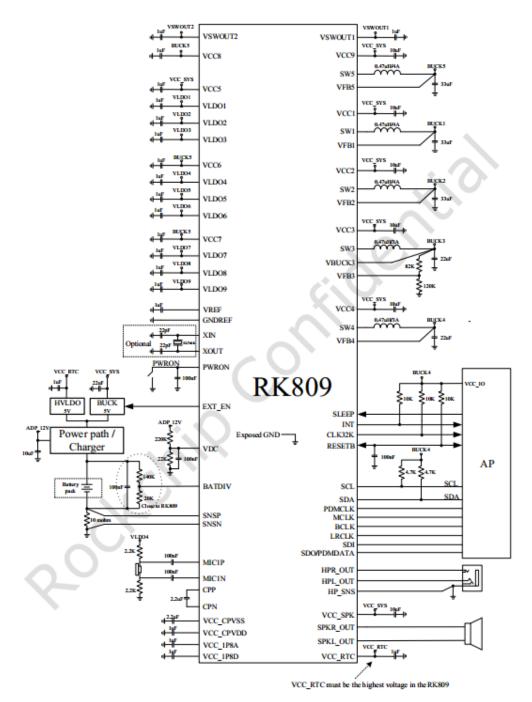

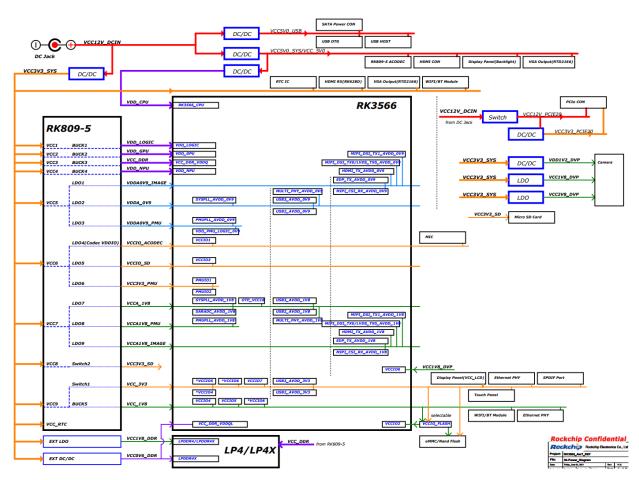

Figure 1-3 RK3566 RK809-5 Application Block Diagram

# 2 Hardware Design Recommendation

# 2.1 Minimum System Design

# 2.1.1 Clock Circuit

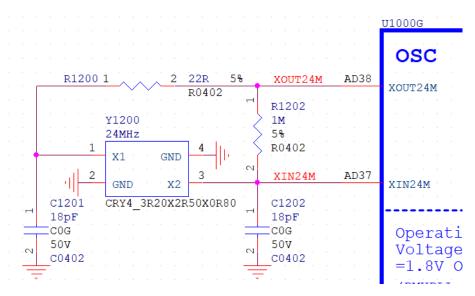

RK3566 internal oscillator circuit and the external 24MHz crystal together constitute the system clock circuit. The recommended crystal connection mode and device parameters are shown in Figure 2-1. The 22ohm resistor connected in series in XOUT24M network must be retained to limit the current and prevent overdrive. Do not change the 1M resistor between XOUT24M and XIN24M networks.

Figure 2-1 RK3566 Crystal Implementation

# A Note

The selected capacitor needs to match the crystal load capacitor, and the material is recommended to be NPO/COG. It is recommended to use 4-Pin SMT crystals, in which two GND pins are fully connected to the ground to enhance the anti-ESD interference ability of the system clock. 18pF is the capacitance value of crystal used by RK, not a general value.

The system clock can also be generated by an external oscillator circuit with a clock amplitude of 1.8V. The clock is input through the XIN24M pin, and the XOUT24M pin is left floating. The clock parameters are shown in the following table 2-1:

| Doromotor             | Spec.     |      |      | Description               |

|-----------------------|-----------|------|------|---------------------------|

| Parameter             | Min.      | Max. | Unit | Description               |

| Frequency             | 24.000000 |      | MHz  |                           |

| Frequency Tolerance   | +/-20     |      | ppm  | frequency tolerance range |

| Clock Amplitude       | 1.8       |      | V    | Peak-to-Peak value        |

| Operating Temperature | -20 80    |      | °C   |                           |

| ESR                   | / 40      |      | Ohm  |                           |

Table 2-1 RK3566 24mhz Digital Clock Source

In standby state, RK3566 can reduce the system power consumption by reducing the system clock frequency. At this time, you can use the PVTM (Process Voltage Temperature Monitor) module inside the chip PMU to provide 32.768k clock, or the external input 32.768k clock can be used. In the case of extreme power consumption requirements for deep sleep, you should choose to use an external clock, which is input from the CLK32K\_IN pin.

In the standby state, it supports IO interrupt wake-up in the power domains of PMUIO0, PMUIO1 and PMUIO2. If the required wake-up source is related to the 24MHz clock, the 24MHz clock cannot be turned off.

The external 32.768KHz RTC clock parameters are shown as below table:

| Parameter                |           | Spec.   | Description |                                                               |  |

|--------------------------|-----------|---------|-------------|---------------------------------------------------------------|--|

| Parameter                | Min. Max. |         | Unit        | Description                                                   |  |

| Frequency                | 32.768000 |         | kHz         |                                                               |  |

| Frequency<br>Tolerance   | +/-30     |         | ppm         | frequency tolerance range                                     |  |

| Clock<br>Amplitude       | 0.65*VDD  | VDD+0.3 | V           | VDD indicates the power voltage of the<br>PMUIO2 power domain |  |

| Operating<br>Temperature | -20       | 80      | °C          |                                                               |  |

| Duty Ratio               | 50        |         | %           |                                                               |  |

Table 2-2 RK3566 32.768khz Clock Requirement

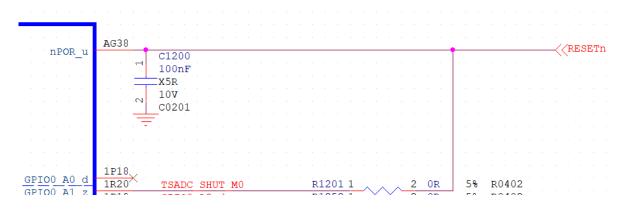

# 2.1.2 Reset Circuit

The hardware reset of the RK3566 is input by the nPOR (RESET) pin, and the low level is active. In order to ensure the stability and normal operation of the chip, the minimum reset time required is 100 cycles of the 24MHz main clock, that is, which means at least 4us or more.

The reset signal needs to be connected in parallel with a 100nF capacitor close to the pin to eliminate jitter on the reset signal, enhance anti-interference ability, and prevent abnormal system reset caused by false trigger. The pull up level of the RESET pin should be consistent with the IO power domain (PMUIO1) where the nPOR pin is located.

Refer to the PMIC RK809-5 or RK817-5 power supply solution. After each power supply of the default output of the PMIC is powered on, the RESET pin will change the output level from low to high to complete the RESET action after a delay(ensure the power is all ready). When the PMIC is in working or SLEEP mode, if the RESET pin level is pulled low, the PMIC will restart. The power-on sequence of this restart is the same as the default.

If the matching PMIC is not used in the design and the power supply is realized by discrete devices, an

independent reset IC should be selected for RK3566 or the reset signal should be obtained from other chips.

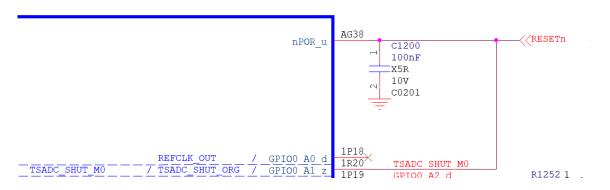

Related circuits are shown in the figure. During layout, keep away from interference signals, interference devices, metal connectors, and edges of the PCB board. Make a ground guard for signals, and drill vias in the ground path with a interval distance of no more than 300mil.

Figure 2-2 RK3566 Reset Input

# 2.1.3 Watchdog/TSADC Circuit

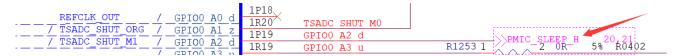

RK3566 integrates a Watchdog Timer. When a reset signal is generated, a low level will output from TSADC\_SHUT\_M0 or TSADC\_SHUT\_M1 pin, and resets RK3566 by hardware.

RK3566 integrates two TSADC(Temperature-sensor ADC) modules. When the internal temperature of the chip exceeds the threshold, the internal TSHUT signal can be sent to the CRU module to reset the RK3566. It can also output low level through TSADC\_SHUT\_M0 or TSADC\_SHUT\_M1 pin to reset RK3566 by hardware.

As shown in the figure 2-2, the TSADC\_SHUT\_M0 is connected to the RESETn network.

# 2.1.4 PMU Circuit

In order to meet the requirement of low power consumption products, RK3566 has designed a power management unit (PMU) to control and manage the internal power supply of the chip.

It should be noted that some functions or modules cannot work in the sleep state. For a detailed list of divisions, please refer to the description of the voltage domain (VD), power domain (PD) and related descriptions in the PMU chapter of the TRM document.

## 2.1.5 System Boot Sequence

RK3566 supports multiple booting ways. After the system is reset, the embedded boot code will automatically boot in the following order. The priority from high to low as below:

- Serial Nor Flash (FSPI)

- Serial Nand Flash (FSPI)

- Nand Flash

- eMMC Flash

- SDMMC Card

If there is no firmware in the memory medium, when connecting to the PC through the USB OTG0 interface, a Maskrom device will be found in the burning tool (the corresponding driver needs to be installed), and the firmware

can be burned at this time

# 2.1.6 System Initialization Configuration Signal

There are two important signals in RK3566 that will affect the system boot configuration, which need to be configured and kept stable before power-on. They are:

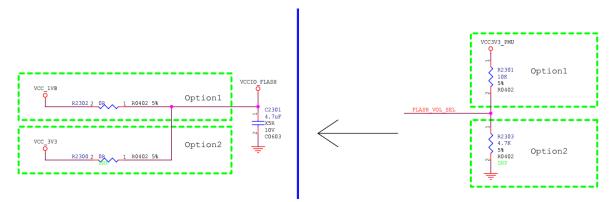

- Level configuration pin FLASH\_VOL\_SEL for VCCIO2 (FLASH) power domain;

- JTAG/SDMMC multiplexing function control pin SDMMC0\_DET;

After the system reset, the chip will configure the default power-on function of the corresponding module according to the input level of the two pins.

The I/O level mode of the RK3566 VCCIO2 power domain requires hardware configuration. Because the power domain belongs to the FLASH power domain, which affects the system boot. When the system power on, the default level mode must be specified by hardware configuration and cannot be adjusted by register operation. The following figure shows the configuration.

• When the I/O level of VCCIO2 and the flash interface is 1.8V, the FLASH\_VOL\_SEL pin must be kept high level during the reset;

• When the I/O level of VCCIO2 and the flash interface is 3.3V, the FLASH\_VOL\_SEL pin must be kept low level during the reset;

The pin configuration must match the actual IO power supply of the external memory interface to prevent system stability or damage

Figure 2-3 Correspondence Between RK3566 FLASH VOL SEL Pin Level And VCCIO2 Status

RK3566 reuses JTAG function and SDMMC function together to reduce IO pin count and take into account the convenience of the complete machine debugging. The SDMMC0\_DET pin is used to switch the output function. Therefore, this pin must be configured before power-on. Otherwise, the debugging during the boot period will be affected if JTAG has no output, and SDMMC0 has no output will affects SDMMC boot.

• SDMMC0\_DET pin detects that the level is high, the IO switches to the JTAG function;

• SDMMC0\_DET detects that the level is low (normal state of SD card insertion, and the PIN is pulled down by SD card slot), the IO function is switched to SDMMC;

The pin is shown as below:

| / CDT00 14   | AF37 | SDMMC0 DET L |

|--------------|------|--------------|

| / GPIOO A4 u | AG37 |              |

Figure 2-4 RK3566 SDMMC0/JTAG Reused Control Pin

The two pins configurations are shown in below table:

| Signal Name   | Internal Pull<br>Up/Down | Description                                                                                                                                                                                                                                              |

|---------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLASH_VOL_SEL | pull up                  | <ul><li>FLASH (VCCIO2) power domain IO supply configuration pin:</li><li>0: IO level mode is 3.3V;</li><li>1: IO level mode is 1.8V;</li></ul>                                                                                                           |

| SDMMC0_DET    | pull up                  | <ul> <li>JTAG function selection pin:</li> <li>0: recognized as sd card insertion, SDMMC/JTAG/UART pin reused as SDMMC function.</li> <li>1: recognized as SD card not insertion, SDMMC/JTAG/UART pin reused as JTAG/UART function (default).</li> </ul> |

| Table 2-3 RK3566 System Initialization | Configuration Signal Description |

|----------------------------------------|----------------------------------|

|----------------------------------------|----------------------------------|

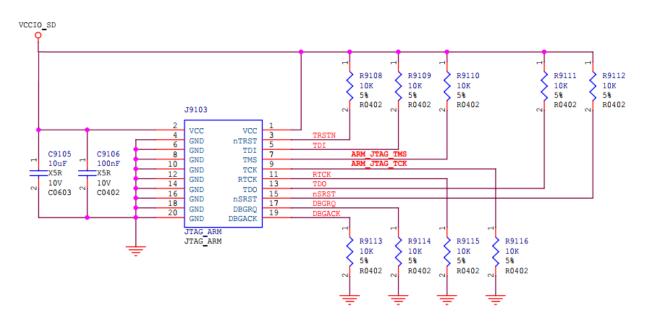

# 2.1.7 JTAG Debug Circuit

The ARM\_JTAG interface of RK3566 conforms to the IEEE1149.1 standard. PC can connect to the DSTREAM emulator through SWD mode (two-line mode) to debug ARM Core inside the chip. At the beginning of the design, it is recommended to reserve test points for these two signals.

Before connecting the emulator, ensure that the SDMMC0\_DET pin is at a high level, otherwise the JTAG debugging mode cannot be entered. The configuration of this pin is described in the previous section. The ARM\_JTAG interface description is as follows:

Table 2-4 RK3568 JTAG debug interface signal

| Signal name  | Description                            |  |

|--------------|----------------------------------------|--|

| ARM_JTAG_TCK | JTAG clock input in SWD mode           |  |

| ARM_JTAG_TMS | JTAG data input and output in SWD mode |  |

The connection method of JTAG and the definition of standard connector pins are shown in the figure below. Generally, only need to reserve test points according to the reference schematic for the first version. There is no need to reserve for the stable version.

Figure 2-5 RK3566 JTAG Connection Circuit In SWD Mode

The MCU\_JTAG module of RK3566 is temporarily closed to the public and no special treatment is required.

# 2.1.8 UART Debug Circuit

For details about this section, see section "Debugging UART Circuits"

# 2.1.9 DDR Circuit

# 2.1.9.1 DDR Controller Introduction

RK3566 DDR controller interface supports JEDEC SDRAM standard interface, the controller has the following features

- Support DDR3/DDR3L/LPDDR3/DDR4/LPDDR4/LPDDR4X standards;

- In DDR3/DDR3L/DDR4 interface mode, supports a 32-bit data bus width, 2 ranks (chip selection), and a maximum address of 8GB;

- In LPDDR3/LPDDR4/LPDDR4X interface mode, it supports a 32-bit data bus width, 4 ranks (chip selection), and a maximum address of 8GB;

- Support low power consumption modes such as Power Down and Self Refresh;

## 2.1.9.2 DDR Topology and Connection Guide

In order to simplify user design of DDR and ensure system reliability, the official layout template is provided for mainstream DDR chip and types, which users can refer to. The reference to the schematic and template must be strictly consistent, including power decoupling capacitors.

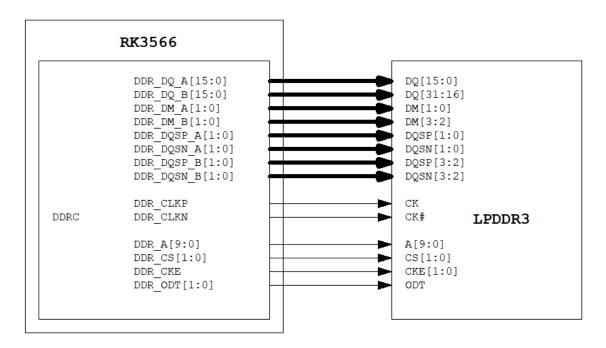

Taking LPDDR3 as an example, the SDRAM topology of RK3566 is shown in the following figure, and the topology of other DDR particles refer to the specific schematic diagram.

Figure 2-6 RK3566 LPDDR3 Topological Structure

For customers who need to do DDR Layout by themselves, the following limitations should be noted:

- DDR3/DDR3L:

- Support the whole group swap between Byte. Support DQ swap within a Byte group.

- The CA order cannot be swapped and must be assigned according to the reference schematic.

- If you want to support templates compatible with 16bit/32bit, you must use the template provided by RK, and changes are not allowed.

- LPDDR3

- It is necessary to maintain the one-to-one correspondence between D0-D7 of the DDR terminal and D0-D7 of the RK3566 LPDDR3 controller, and ensure the one-to-one correspondence between the associated DQS and DM, this Byte group does not support adjustment.

- Other Byte support whole group exchange.

- DQ in other bytes support swap.

- The CA order can not interchangeable and must be assigned according to the reference schematic.

- DDR4

- Support the whole group swap between Byte groups.

- Support DQ swap within a Byte group.

- The CA order cannot be swapped and must be assigned according to the reference schematic.

- If you want to support templates compatible with 16bit/32bit, you must use the template provided by RK, and changes are not allowed.

- LPDDR4/LPDDR4X

- The DQ and CA order cannot be swap and must be assigned according to the reference schematic.

# 2.1.9.3 Description of DQ Connection of LPDDR3

As mentioned in the previous section, the D[7:0] Byte of LPDDR3 does not support adjustment. Please keep the corresponding relationship between the D[7:0] of DDR and the DQ of RK3566, as well as the corresponding

relationship between the associated DQS, as shown in the figure below. Do not change.

# LPDDR3 1x32bit

Figure 2-7 DQ[7:0] connection description of LPDDR3 particle

# 2.1.9.4 DDR Power Up Sequence Requirement

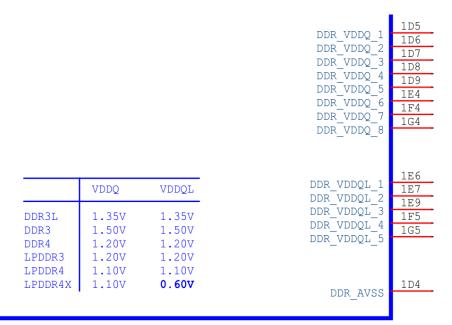

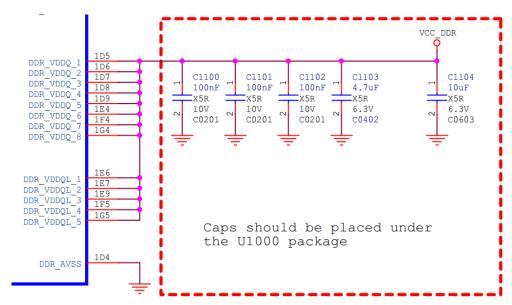

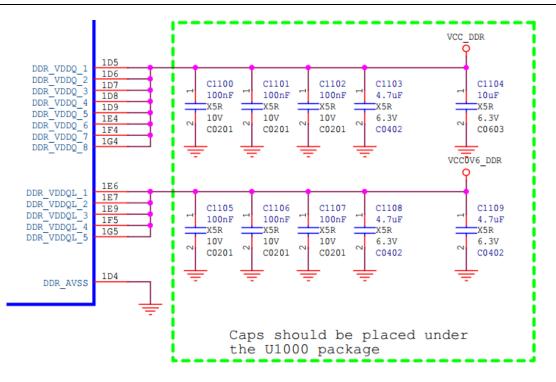

For DDR3/DDR3L/LPDDR3/DDR4/LPDDR4 type memory, RK3566 DDR controller has only one set of power supply: DDR\_VDDQ, DDR\_VDDQ is used for DDR controller's Core power supply interface I/O power supply and output buffer power supply

For LPDDR4X type memory, RK3566 DDR controller needs two sets of power supplies: DDR\_VDDQ and DDR\_VDDQL, the latter is the power supply for the output buffer.

The supply voltage of VDDQ/VDDQL corresponding to different particles is shown in the figure:

Figure 2-8 Different DDR particles correspond to VDDQ/VDDQL supply voltage

SDRAM usually include two sets of power supplies. Please refer to the JEDEC standard of the respective SDRAM chip for the power-on sequence. A brief introduction is as follows:

The power-on sequence of DDR3/DDR3L SDRAM is shown in the figure below:

- Apply power (RESET# is recommended to be maintained below 0.2 x VDD; all other inputs may be undefined). RESET# needs to be maintained for minimum 200 us with stable power. CKE is pulled "Low" anytime before RESET# being de-asserted (min. time 10 ns). The power voltage ramp time between 300 mv to VDDmin must be no greater than 200 ms; and during the ramp, VDD > VDDQ and (VDD - VDDQ) < 0.3 volts.</li>

- · VDD and VDDQ are driven from a single power converter output, AND

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side. In addition, VTT is limited to 0.95 V max once power ramp is finished, AND

- Vref tracks VDDQ/2.

OR

- · Apply VDD without any slope reversal before or at the same time as VDDQ.

- · Apply VDDQ without any slope reversal before or at the same time as VTT & Vref.

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side.

#### Figure 2-9 DDR3 SDRAM's power-on sequence

The power-on sequence of LPDDR3 SDRAM is shown in the figure below:

| After         | Applicable Conditions                                                      |

|---------------|----------------------------------------------------------------------------|

| Ta is reached | $V_{\rm DD1}$ must be greater than $V_{\rm DD2}$ —200mV                    |

|               | $V_{\rm DD1}$ and $V_{\rm DD2}$ must be greater than $V_{\rm DDCA}$ —200mV |

|               | $V_{\rm DD1}$ and $V_{\rm DD2}$ must be greater than $V_{\rm DDQ}$ —200mV  |

|               | $V_{ m Ref}$ must always be less than all other supply voltages            |

Figure 2-10 LPDDR3 SDRAM's power-on sequence

The power-on sequence of DDR4 SDRAM is shown in the figure below:

- Apply power (RESET\_n is recommended to be maintained below 0.2 x VDD; all other inputs may be undefined). RESET\_n needs to be maintained for minimum 200us with stable power. CKE is pulled " Low" anytime before RESET\_n being de-asserted (min. time 10ns). The power voltage ramp time between 300mV to V<sub>DD</sub> min must be no greater than 200ms; and during the ramp, V<sub>DD</sub> ≥ V<sub>DDQ</sub> and (V<sub>DD</sub>-V<sub>DDQ</sub>) < 0.3volts. VPP must ramp at the same time or earlier than VDD and VPP must be equal to or higher than VDD at all times.</li>

- · V<sub>DD</sub> and V<sub>DDQ</sub> are driven from a single power converter output, AND

• The voltage levels on all pins other than  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{SS}$ ,  $V_{SSQ}$  must be less than or equal to  $V_{DDQ}$  and  $V_{DD}$  on one side and must be larger than or equal to  $V_{SSQ}$  and  $V_{SS}$  on the other side. In addition,  $V_{TT}$  is limited to TBDV max once power ramp is

- finished, AND

- VrefCA tracks TBD

- or

- Apply  $V_{\text{DD}}$  without any slope reversal before or at the same time as  $V_{\text{DDQ}}$

- Apply V\_{DDQ} without any slope reversal before or at the same time as V\_TT & VrefCA.

- · Apply VPP without any slope reversal before or at the same time as VDD.

• The voltage levels on all pins other than  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{SS}$ ,  $V_{SSQ}$  must be less than or equal to  $V_{DDQ}$  and  $V_{DD}$  on one side and must be larger than or equal to  $V_{SSQ}$  and  $V_{SS}$  on the other side.

Figure 2-11 DDR4 SDRAM's power-on sequence

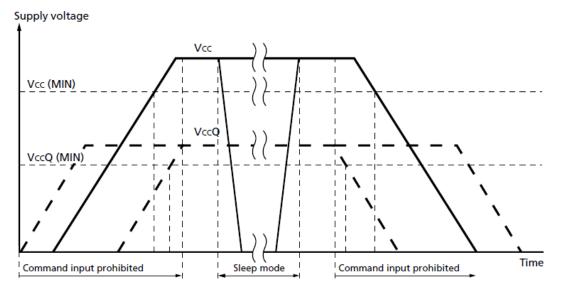

The power-on sequence of LPDDR4 SDRAM is shown in the figure below:

While applying power (after Ta), RESET\_n is recommended to be LOW (≤0.2 x V<sub>DD2</sub>) and all other inputs must be between VILmin and VIHmax. The device outputs remain at High-Z while RESET\_n is held LOW. Power supply voltage ramp requirements are provided in Table 5. V<sub>DD1</sub> must ramp at the same time or earlier than V<sub>DD2</sub>. V<sub>DD2</sub> must ramp at the same time or earlier than V<sub>DD0</sub>.

| Table 5 — Voltage Ramp Conditions |                                                        |  |

|-----------------------------------|--------------------------------------------------------|--|

| After Applicable Conditions       |                                                        |  |

| Ta is reached                     | V <sub>DD1</sub> must be greater than V <sub>DD2</sub> |  |

|                                   | $V_{DD2}$ must be greater than $V_{DDQ}$ - 200 mV      |  |

NOTE 1 Ta is the point when any power supply first reaches 300 mV.

NOTE 2 Voltage ramp conditions in Table 5 apply between Ta and power-off (controlled or uncontrolled).

NOTE 3 Tb is the point at which all supply and reference voltages are within their defined ranges.

NOTE 4 Power ramp duration tINIT0 (Tb-Ta) must not exceed 20ms.

NOTE 5 The voltage difference between any of V<sub>SS</sub> and V<sub>SSQ</sub> pins must not excess 100 mV.

Figure 2-12 LPDDR4 SDRAM's Power-on Sequence

# 2.1.9.5 DDR RZQ Signal Processing

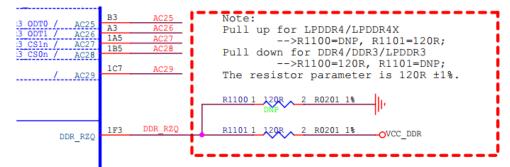

Noted that the connection method of DDR\_RZQ is different due to the type of DDR chip:

When using DDR3/DDR3L/DDR4/LPDDR3, DDR\_RZQ needs to be pulled down through a 1% precision 1200hm resistor;

When using LPDDR4/LPDDR4X, DDR\_RZQ should be pulled up to the VCC\_DDR power supply through a 1% precision 120ohm resistor.

Figure 2-13 Description of DDR RZQ Connection

# 2.1.9.6 DDR VREFOUT Voltage Output Connection Usage

DDR PHY of RK3566 can provide voltage to the VREFDQ or VREFCA of the SDRAM chip. The specific connection usage for different SDRAM are as follows:

- DDR3/DDR3L: provide VREFDQ for DDR3/DDR3L, the default voltage is 0.75/0.675V, the output voltage value can be adjusted through registers; VREFCA of DDR3/DDR3L is still obtained through voltage divider circuit of VCC\_DDR;

- LPDDR3: provide VREFDQ for LPDDR3, the voltage is related to ODT configuration, the output voltage value can be adjusted through registers; VREFCA of LPDDR3 is still obtained through voltage divider circuit of VCC\_DDR;

- DDR4: provide VREFCA for DDR4, the default voltage is 0.6V, and the voltage value can be adjusted through the register;

- LPDDR4/LPDDR4X: No need to use.

# 2.1.9.7 DDR Support List

The maximum working frequency of RK3566 DDR is greatly affected by layout. Most of the official templates can support the maximum working frequency up to 1056MHz. For the specific rate, please refer to the relevant instructions of the DDR template file in the release information.

It is recommended that customers select the official DDR template for design to ensure the reliability and stability of the system. If you have to design by yourself, please consult RK for more detailed layout restrictions.

For the DDR chip Support List, please refer to the RK DDR Support List, which can be downloaded on the Redmine platform:

https://redmine.rockchip.com.cn/projects/fae/documents?tdsourcetag=s\_pctim\_aiomsg

# 2.1.10 eMMC Circuit

# 2.1.10.1 eMMC Controller Introduction

The features of RK3566 eMMC controller are as follows:

- Compatible with standard iNAND interface;

- Compatible with eMMC specification 4.41, 4.51, 5.0 and 5.1

- Support three data bus widths of 1-bit, 4-bit and 8-bit;

- Support HS200 mode;

- Support CMD Queue;

# 2.1.10.2 eMMC Topology and Connection Guide

Recommended pull up/down and the matching design of eMMC interface are as Table 2-5. The pull-up resistance of D0 and CMD signals must be reserved, and the pull-down resistance of DATA\_STROBE signal is recommended to be reserved.

The capacitance of the VDDi pin of the eMMC chip must be 2.2uF, or a larger capacitance value as required by the specific particle specification.

| Signal           | Internal pull<br>up/down | Connection method                                                                                                | Description<br>(chip side)   |

|------------------|--------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------|

| eMMC_DQ[7:0]     | pull up                  | Direct connection, D0 pull-up with a<br>external 10K ohm resistor, other data<br>use the inside pull-up resistor | eMMC data send/receive       |

| eMMC_CLK         | pull down                | connect 220hm resistor in series with RK3566 output end.                                                         | eMMC clock output            |

| eMMC_DATA_STROBE | pull down                | Direct connection; Reserve pull-down resistors                                                                   | eMMC clock input             |

| eMMC_CMD         | pull up                  | Direct connection; Pull with external<br>10K resistance                                                          | eMMC command<br>send/receive |

# Table 2-5 RK3566 eMMC Interface Design

#### 2.1.10.3 eMMC Power Up Sequence Requirement

The eMMC controller of RK3566 belongs to VCCIO2 power domain, with only one group of power supply, so it is no timing sequence requirements. But it should be noted that the level of the power supply needs to match the FLASH VOL SEL state configuration mentioned above.

The eMMC has two sets of power supplies, refer to JEDEC standard for power-on sequence:

- VCC and VCCQ have no sequential requirements on the power-on sequence;

- VCC and VCCQ must be powered on and maintain a stable working voltage before the CMD command is generated;

- After the chip enters sleep mode, RK3566 can turn off the VCC power to reduce power consumption;

- Before the chip is awakened from sleep mode, the VCC power supply must be powered on and maintain a stable operating voltage;

Figure 2-14 eMMC power up/down sequence

#### 2.1.10.4 MASKROM Download Test Point Description

Please reserve the test point of eMMC D0/CLK in the development process to avoid the failure of entering the Maskrom download mode while the firmware fails. Refer to the reference schematic for the reservation method. The branch of the test point and signal routing should be strictly shortened during layout.

## 2.1.10.5 eMMC Support List

RK3566 eMMC support list please refer to *RK eMMC Support List* released by Rockchip. The document can be downloaded from redmine through below link:

https://redmine.rockchip.com.cn/projects/fae/documents?tdsourcetag=s\_pctim\_aiomsg

# 2.1.11 Nand Flash Circuit Design

# 2.1.11.1 Nand Flash Controller Introduction

- RK3568 Nand Flash controller has the following features:

- Supports SLC, MLC, TLC Nand Flash;

- Supports asynchronous flash memory interface with 8-bit data width;

- Supports ONFI synchronous flash memory interface with 8-bit data width;

- Supports Toggle flash memory interface with 8-bit data width;

- Support 16-bit BCH/ECC.

#### 2.1.11.2 Nand Flash Topology and Matching Design

Recommended pull up/down and the matching design of Nand Flash interface are as follows, the pull-up resistors of FLASH RDY/FLASH CS0n/FLASH CS1n must be reserved:

| Signal       | Internal pull<br>up/down | Connection Method                 | Description (chip side)      |

|--------------|--------------------------|-----------------------------------|------------------------------|

| FLASH_D[7:0] | pull up                  | direct connection                 | Nand Flash data send/receive |

| FLASH_WRn    | pull up                  | direct connection                 | Nand Flash Writing enable    |

| FLASH_DQS    | pull down                | direct connection                 | Nand Flash data strobe       |

|              |                          | direct connection                 | Nand Flash                   |

| FLASH_CLE    | pull down                |                                   | Command latch enabled        |

| FLASH_WPn    | pull down                | direct connection                 | Nand Flash write protected   |

|              |                          | direct connection                 | Nand Flash                   |

| FLASH _ALE   | pull down                |                                   | address latch enabled        |

| ELASH DDV    | au11 um                  | direct connection, external pull- | Nand Flash                   |

| FLASH _RDY   | pull up                  | up with a 4.7K ohm resistor       | Ready/busy state             |

| FLASH_RDn    | pull up                  | direct connection                 | Nand Flash read enable       |

| ELASIL CSO.  |                          | direct connection; external pull- | Nand Flash                   |

| FLASH _CS0n  | pull up                  | up with a 4.7K ohm resistor       | Chip select 0                |

|              |                          | direct connection; external pull- | Nand Flash                   |

| FLASH_CS1n   | pull up                  | up with a 4.7K ohm resistor       | Chip select 1                |

#### Table 2-6 RK3566 Nand Flash interface design

# 2.1.11.3 Nand Flash Power up Sequence Requirement

The Nand Flash controller of RK3566 chip belongs to the VCCIO2 power domain, only one power supply, so there is no sequence requirements. But it should be noted that the level of the power supply needs to match the FLASH\_VOL\_SEL state configuration mentioned above.

Nand Flash chip has two sets of power supplies, please refer to JEDEC standard for power-on sequence.

Once V<sub>CC</sub> and VccQ reach the V<sub>CC</sub> minimum and VccQ minimum values, respectively, listed in Table 5 and power is stable, the R/B\_n signal shall be valid after RB\_valid\_Vcc and shall be set to one (Ready) within RB\_device\_ready, as listed in Table 16. R/B\_n is undefined until 50  $\mu$ s has elapsed after V<sub>CC</sub> has started to ramp. The R/B\_n signal is not valid until both of these conditions are met.

| Parameter       | Raw NAND | EZ NAND |

|-----------------|----------|---------|

| RB_valid_Vcc    | 10 µs    | 250 µs  |

| RB_device_ready | 1 ms     | 2 ms    |

| Table 16 | R/B_n Power-on Requirements | í |

|----------|-----------------------------|---|

|----------|-----------------------------|---|

During power-on, VccQ shall be less than or equal to Vcc at all times. Figure 19 shows VccQ ramping after Vcc, however, they may ramp at the same time.

Figure 2-15 Nand Flash power-on/down sequence

#### 2.1.11.4 Nand Flash Download Test Point Description

Please reserve the test point of FLASH D0/CLK in the development process to avoid the failure of entering the Maskrom download mode while the firmware fails. Refer to the reference schematic for the reservation method. The branch of the test point and signal routing should be strictly shortened during layout.

#### 2.1.11.5 Nand Flash Support List

For RK3566 Nand Flash support list, please refer to the document "RK Nand Flash Support List", which can be downloaded from Rockchip redmine platform:

https://redmine.rockchip.com.cn/projects/fae/documents?tdsourcetag=s pctim aiomsg

# 2.1.12 FSPI Flash Circuit

#### 2.1.12.1 FSPI Controller Introduction

FSPI is a flexible serial interface controller. There is a FSPI controller in RK3566, which can be used to connect FSPI devices.

The features of RK3566 FSPI controller are as follows:

- Support serial NOR and NAND FLASH;

- Support SDR mode; support single/dual/four-line mode;

- Support two chip select

# 2.1.12.2 FSPI Topology and Connection Guide

Recommended pull up/down and the matching design of FSPI Flash interface are as shown in Table2-7, where the external pull-up resistors of the FSPI\_D2/FSPI\_D3 pins must be reserved:

| Signal      | Internal pull up/down            | Connection Method                | Description (chip side)  |

|-------------|----------------------------------|----------------------------------|--------------------------|

| FSPI_D[3:0] | D2 pull down<br>D0/D1/D3 pull up | Direct connection                | SPI data send/receive    |

| FSPI0_CLK   | Pull down                        | Series connect<br>220hm resistor | SPI clock output         |

| FSPI0_CS0n  | Pull up                          | Direct connection                | SPI chip select signal 0 |

| FSPI0_CS1n  | Pull down                        | Direct connection                | SPI chip select signal 1 |

Table 2-7 RK3566 FSPI Interface Design

## 2.1.12.3 FSPI Support List

The FSPI Flash controller of RK3566 chip belongs to the VCCIO2 power domain, only one power supply, so there is no sequence requirements. But it should be noted that the level of the power supply needs to match the FLASH\_VOL\_SEL state configuration mentioned above.

SPI FLASH chip only has one set of power supplies, so there is no timing requirement.

## 2.1.12.4 FSPI Download Test Point Description

Please reserve the test point of FSPI D0/CLK in the development process to avoid the failure of entering the Maskrom download mode while the firmware fails. Refer to the reference schematic for the reservation method. The branch of the test point and signal routing should be strictly shortened during layout.

# 2.1.12.5 SPI Support List

RK3566 SPI support list, please refer to the document *RK SpiNor and SLC Nand Support List*, which can be downloaded from Rockchip redmine platform:

https://redmine.rockchip.com.cn/projects/fae/documents?tdsourcetag=s\_pctim\_aiomsg

FSPI\_CS1n is multiplexed with the DATA STROBE pin of eMMC, while other pins of FSPI have no multiplexing relationship with eMMC. Therefore, when FSPI only uses one chip select, eMMC can be used at the same time. For example, use FSPI as boot and eMMC as large capacity storage.

# 2.1.13 GPIO Circuit

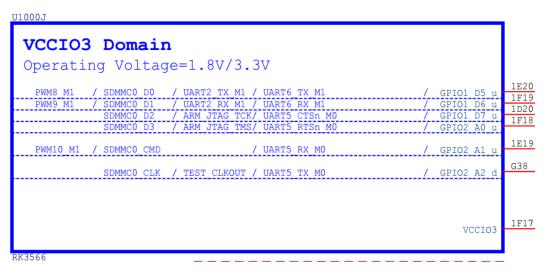

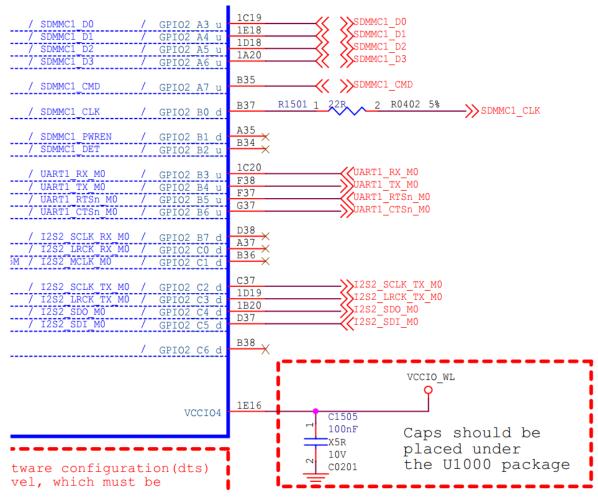

There are 10 independent IO power domains in RK3566, which are PMUIO[0:2] and VCCIO[1:7]. Among them:

- PMUIO0 and PMUIO1 are fixed level power supply domain and cannot be configured;

- PMUIO2 and VCCIO1, VCCIO[3:7] power supply domains require that the hardware power supply voltage

match the configuration of the software:

- When the hardware IO level is connected to 1.8V, the software voltage should be configured to 1.8V;

- When the hardware IO level is connected to 3.3V, the software voltage should be configured to 3.3V;

- VCCIO2 Power domain does not need a software configuration, but the hardware power supply voltage must match the FLASH VOL SEL status:

- When the VCCIO2 power supply is 1.8V, the FLASH\_VOL\_SEL pin must remain high level;

■ When the VCCIO2 power supply is 3.3V, the FLASH\_VOL\_SEL pin must be kept low level;

Otherwise, there will be the following risks:

- Software configuration is 1.8V while hardware power supply is 3.3V, which will make the IO in an overvoltage state, and the IO will be damaged if it works for a long time;

- Software configuration is 3.3V while hardware power supply is 1.8V, IO function will be abnormal;

If the power domain is changed in the customer project, voltage configurations must be updated. All kinds of documents from RK have emphasized this note. Please ask the customer's software and hardware engineer to review the correctness of the voltage configuration of their respective projects.

Reference documents:

- 1) DTS configuration notes: https://redmine.rock-chips.com/documents/106

- 2) Checklist: Rockchip\_RK3566\_IO\_Power\_Domain\_Checklist\_V1.0\_CN.xlsx

#### 2.1.13.1 GPIO Pins Description

Take the pin GPIO2\_A3\_u as an example, where \_u indicates that the default reset state of this IO is internal pull-up; similarly, \_d indicates that the default state is internal pull-down, and \_z indicates that the default state is high-impedance state.

Except for the boot-related GPIO mentioned above, the default state of other IOs are all inputs after reset.

For function pins name with the suffix \_M0/\_M1/\_M2, it means that the same function pin is multiplexed on different IOs, and only one of them can be used at the same time. And it should be noted that the same group of function pins can only be used in combination with the same suffix. For example, when selecting the UART2 function, you can choose the combination of UART2\_TX\_M0 and UART2\_RX\_M0, or the combination of UART2\_TX\_M1 and UART2\_RX\_M1. Different multiplexing suffix IO cannot be selected for combination.

### 2.1.13.2 GPIO Driving Capability

In RK3566, GPIO provides multiple levels of adjustable drive strength, which are Level 0-5. Some GPIOs can achieve Level 0-11 adjustment levels. For details, please refer to the *RK3566\_PinOut* document. In addition, depending on the different type of GPIO, the initial default drive strength is different. Please refer to the chip TRM for configuration modification. You can also refer to the "Support Drive Strength" and "Default IO Drive Strength" columns in Table 5 in the *RK3566\_PinOut* document.

# 2.1.13.3 GPIO Power

The power pin of GPIO power domain is described as below:

#### Table 2-8 RK3566 GPIO power pin description

| Power<br>domain | GPIO Type  | Pin Name        | Description                                          |

|-----------------|------------|-----------------|------------------------------------------------------|

| PMUIO0          | Fixed 1.8V | PMUPLL_AVDD_1V8 | 1.8V Only IO supply for this GPIO domain (group).    |

| PMUIO1          | Fixed 3.3V | PMUIO1          | 3.3V Only IO supply for this GPIO domain (group).    |

| PMUIO2          | 1.8V/3.3V  | PMUIO2          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

| VCCI01          | 1.8V/3.3V  | VCCI01          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

| VCCIO2          | 1.8V/3.3V  | VCCIO2          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

| VCCIO3          | 1.8V/3.3V  | VCCIO3          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

| VCCIO4          | 1.8V/3.3V  | VCCIO4          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

| VCCIO5          | 1.8V/3.3V  | VCCIO5          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

| VCCIO6          | 1.8V/3.3V  | VCCIO6          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

| VCCIO7          | 1.8V/3.3V  | VCCIO7          | 1.8V or 3.3V IO supply for this GPIO domain (group). |

PMUIO0 and PMUIO1 are fixed-level power domains and cannot be configured. Other IO domains can be configured.

The power supply ripple of the GPIO power domain is required to be within  $\pm 5\%$ , and at least one 100nF decoupling capacitor should be placed nearby for each power supply pin. See the reference schematic for the detailed design.

If all IOs in one power domain are not used, then the power domain do not need a power supply, and the corresponding pins can be left floating.

# 2.2 Power Design

# 2.2.1 Minimum System Power Introduction

# 2.2.1.1 Power Requirement

| Module        | Power Pin                       | Description               |  |

|---------------|---------------------------------|---------------------------|--|

| PMU PLL       | PMUPLL_AVDD_0V9、                | PMU PLL power             |  |

|               | PMUPLL_AVDD_1V8                 |                           |  |

| SYSTEM PLL    | SYSPLL_AVDD_0V9、                | System PLL power          |  |

|               | SYSPLL_AVDD_1V8                 |                           |  |

| CPU           | VDD_CPU                         | CPU/ARM Core power        |  |

| GPU           | VDD_GPU                         | GPU power                 |  |

| NPU           | VDD_NPU                         | NPU power                 |  |

| LOGIC         | VDD_LOG                         | SOC logic power           |  |

| PMU LOGIC     | PMU_VDD_LOGIC_0V9               | PMU logic power           |  |

| DDR           | VCC_DDR                         | DDR PHY power             |  |

| GPIO          | PMUIO0、PMUIO1、PMUIO2、           | IO Domain power           |  |

|               | VCCIO1、VCCIO2、VCCIO3、           |                           |  |

|               | VCCIO4、VCCIO5、VCCIO6、VCCIO7     |                           |  |

| SARADC        | SARADC_AVDD_1V8                 | SARADC power              |  |

| OTP           | OTP_VCC18                       | OTP power                 |  |

| USB2.0 PHY    | USB_AVDD1_0V9、USB_AVDD1_1V8、    | USB2.0 PHY power          |  |

|               | USB_AVDD1_3V3、USB_AVDD2_0V9、    |                           |  |

|               | USB_AVDD2_1V8、USB_AVDD2_3V3     |                           |  |

| MULTI PHY     | MULTI_PHY_AVDD_0V9、             | MULTI PHY power (include: |  |

|               | MULTI_PHY_AVDD_1V8              | USB3.0, SATA, PCIe)       |  |

| MIPI CSI PHY  | MIPI_CSI_RX_AVDD_0V9            | MIPI CSI RX PHY power     |  |

|               | MIPI_CSI_RX_AVDD_1V8、           |                           |  |

| MIPI DSI/LVDS | MIPI_DSI_TX0/LVDS_TX0_AVDD_0V9、 | MIPI DSI TX PHY/LVDS      |  |

| PHY           | MIPI_DSI_TX0/LVDS_TX0_AVDD_1V8、 | PHY power                 |  |

|               | MIPI_DSI_TX1_AVDD_0V9           |                           |  |

|               | MIPI_DSI_TX1_AVDD_1V8           |                           |  |

| eDP PHY       | EDP_TX_AVDD_0V9、                | eDP PHY power             |  |

|               | EDP_TX_AVDD_1V8                 |                           |  |

| HDMI PHY      | HDMI_TX_AVDD_0V9、               | HDMI TX PHY power         |  |

|               | HDMI_TX_AVDD_1V8                |                           |  |

#### 2.2.1.2 Power on Sequence

Theoretically, follow the power-on principle of "the same module is powered on low voltage first, and power on high voltage later", "equal voltage in same module is powered on at the same time", and "no timing requirements between different modules". The RESETn should release not be less than 10ms after the last power is stable.

The recommended power-on sequence of the RK3566 is as follows:

$VDDA0V9\_PMU/VDDA\_0V9/VDD\_LOGIC \rightarrow VCCA1V8\_PMU/VCC\_1V8/VCC3V3\_PMU/VDD\_GPU \rightarrow VDD\_CPU \rightarrow VCC\_DDR \rightarrow VCC\_3V3 \rightarrow RESETn$

## 2.2.1.3 Power off Sequence

When the power supply voltage of the PMUIO1 power domain drops below 2.93V, RESETn must be pulled down first, and other power supplies will be powered off.

# 2.2.2 Power Design Recommendation

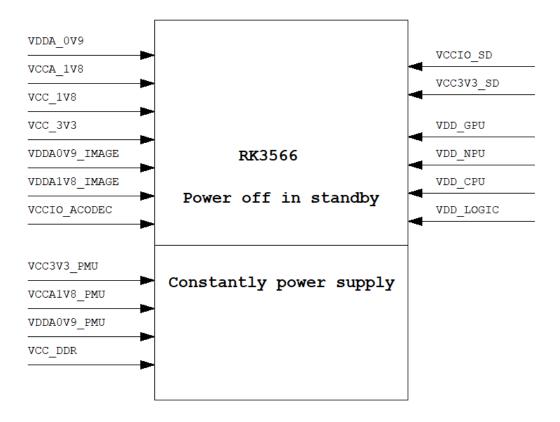

## 2.2.2.1 Standby Circuit Solution

RK3566 system uses the standby solution and the system consists of constant power supply area and power-off in standby area. The two parts are independently powered, as shown in the figure below:

Figure 2-16 RK3566 Standby Circuit Solution

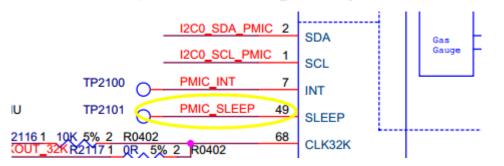

The standby power-down area power supply controls the PMIC to turn off each independent power supply in the standby state through the PMIC\_SLEEP\_H signal.

The power of the constant power supply area is directly provided by the power chip. In the standby state, at least four sets of power supplies should be kept power-up, as shown below:

- VCC\_DDR: Power for DDR self-refresh.

- VDDA0V9\_PMU: Provide power for Logic of PMUIO0 & PMUIO1 & PMUIO2 power domain. Provide power for PMUPLL and CPU OSC to work.

- VCCA1V8\_PMU: Provide IO power for PMUIO1 & PMUIO2 power domain to maintain output status and interrupt response; Provide power for PMUPLL to work.

- VCC3V3\_PMU: Provide IO power for PMUIO1 & PMUIO2 power domain to maintain output status and interrupt response.

The above standby solution can only support IO interrupt wake-up of PMUIO0, PMUIO1 and PMUIO2, and the IO of the other IO Domains will be invalid.

In standby, if you need to support USB HID device wake-up, the USB PHY power supply needs to be retained.

In standby, if you need to support IO interrupt wake-up in VCCIO1, VCCIO2, VCCIO3, VCCIO4, VCCIO5,

VCCIO6, VCCIO7, then the power supply of VDD\_LOGIC and the corresponding IO Domain needs to be retained.

# 2.2.2.2 PLL Power

There are 9 PLLs in the RK3566, which are allocated as follows:

Table 2-10 RK3566 internal PLL Introduction

| Classify            | Quantity | Power            | Standby State            |

|---------------------|----------|------------------|--------------------------|

| PMU/OSC             | 2        | PMUPLL_AVDD_0V9  | Can't turn off the power |

|                     |          | PMUPLL_AVDD_1V8  |                          |

| Modules in the chip | 7        | SYSPLL_AVDD_0V9, | Can turn off the power   |

|                     |          | SYSPLL_AVDD_1V8  |                          |